Seria ELECTRONICĂ și TELECOMUNICAȚII TRANSACTIONS on ELECTRONICS and COMMUNICATIONS

Tom 49(63), Fascicola 2, 2004

# A new approach of op-amp amplifier biasing

Gabriel Oltean<sup>1</sup>, Emilia Sipos<sup>1</sup>, Ioana Oltean<sup>2</sup>

Abstract – A new method to deal with the biasing problem of op-amp amplifier is presented. The purpose is to provide for the students a structured method that highlights the line of reasoning to solve the problem of amplifying a signal with no d.c. component, using an opamp operated from a single power supply. The main idea is: the signal source should see a VTC that allows both positive and negative swing for the signal. Th paper presents the general method and its application for a non-inverting and for an inverting amplifier. Keywords: VTC, bias voltage, equivalent circuit

### I. INTRODUCTION

Although in most of the op-amp amplifier applications the supply is differential, in some cases exist only one power supply (e.g. auto equipments).

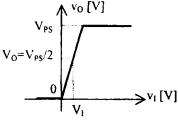

The voltage transfer characteristic-VTC of an op-amp amplifier operated from a single (positive) power supply is the one given in Fig.1. As all of us know, with this VTC we cannot directly amplify a  $v_i(t)$ signal with a zero dc level. The solution is to bias the circuit to operate around a point near the middle of the VTC. In the electronic circuit books [1], [2], [3] is presented only the final solution (applying a dc voltage V<sub>1</sub> to obtaining at the output the dc voltage V<sub>0</sub> in the middle of VTC). The reasoning used to reach that final solution is well hidden for the students. Due to this lack of information, the students are not able to solve the same problem for a new circuit or in another similar situation.

Our idea is to present a structured method to deal with the amplification matter in an op-amp amplifier operated from a single power supply. The method is based on the following idea: the signal source should see a different VTC, so that for a zero input voltage the output should be placed in the middle of the output voltage range.

Fig.1. The VTC of a single supply opamp amplifier

## **II. THE NEW METHOD**

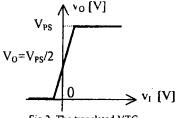

The desired translated VTC looks like the one in Fig.2.

Fig.2. The translated VTC

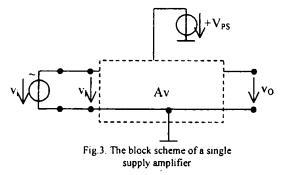

Presentation of the method is much easier to explain on some block schemes. The initial amplifier with VTC given in Fig.1 can be represented by the block

scheme in Fig.3.

The amplifier see to its input a voltage with only the variable component  $v_i$ , so the output voltage will have only a variable component too. The amplifier equations are:

$$v_I = v_i \tag{1}$$

$$\mathbf{v}_O = \mathbf{v}_I \cdot \mathbf{A}_v \tag{2}$$

$$v_O = v_i \cdot A_v \tag{3}$$

$$v_{ij} = v_j \cdot A_j \tag{4}$$

Comparing the Fi\_.1 and Fi\_.2 one can observe that the VTC in the second figure results by horizontally translation of the initial VTC with an appropriate dc voltage, let's name it  $V_{BLAS}$ . This translation is made

Technical University of Cluj -Napoca, Str. C. Daicoviciu 15. 400020, e-mail Gabriel Oltean@bel.utcluj.ro

<sup>&</sup>lt;sup>2</sup> Electrotechnical School Group "Edmond Nicolau", Cluj-Napoca

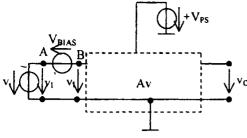

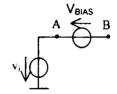

on the x axis and is obtained by series connection of a

Fig.4. The block scheme to translate the VTC

$V_{BIAS}$  source to the input of the amplifier, as it is presented in [4]. The  $V_{BIAS}$  value should be in accordance to the value of the dc voltage needed at the output. Therefore, the value of  $V_{BIAS}$  will be choused such a way to receive for the output voltage a value equal with half of the supply voltage  $V_{PS}$ . The block scheme to obtain the translated VTC (Fig.2) is given in Fig.4.

The amplifier see now to its input a voltage  $v_1$  equal with the sum between the bias voltage  $V_{BIAS}$  and the variable input voltage  $v_1$ . The output voltage  $v_0$  will also have a dc and a variable component.

$$v_I = V_{BIAS} + v_i \tag{5}$$

$$v_O = v_I \cdot A_v = V_{BLAS} \cdot A_v + v_o \cdot A_v \tag{6}$$

Because the dc output voltage must be at the middle of the VTC results that we should have:

$$V_{BLAS} \cdot A_{\nu} = V_{PS} / 2 \tag{7}$$

$$V_{BIAS} = \frac{V_{PS} / 2}{A_v} \tag{8}$$

So, beside the small signal gain also results a dc gain. To improve the operation of the amplifier (reduce the effects of finite input dc offset voltage) it is often a great idea to "roll off" the gain to unity at dc, especially if the amplifier has large voltage gain [3]. This can be done by using a capacitor in the negative feedback path of the amplifier. This capacitor should be placed so that it can be able to play a double role: first, to set the desired a.c. gain  $(A_x)$  (by its short-circuit equivalence in the small signal regime) and second, to set a unitary d.c. gain (by its open-circuit eq...\_len\_e in ...e d...\_g....).

The voltage output equation of the amplifier became:

$$v_O = V_{BIAS} + v_o \cdot A_v \tag{9}$$

To avoid the use of an extra dc voltage source,  $V_{BIAS}$  can be obtained by a resistive voltage divider from  $V_{PS}$  to the ground. For equal resistances the value of  $BIAS re_{--}t_{--} = \frac{1}{PS} = \frac{1}{PS}/2$ . T p v t th c curr t to flow through the input signal source we use a capacitor to insert to the input the  $V_{BIAS}$  dc voltage - see Fig. 5. In the steady state regime (after the ending of the transient regime) this capacitor is charged up

Fig.5. The circuit necessary to obtain the biasing

with  $V_{BIAS}$  and it plays the role of a voltage source, resulting the equivalent scheme in Fig. 6.

Fig.6 The equivalent circuit for the circuit from Fig.5

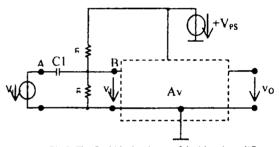

The final block scheme that solves the problem of amplifying a zero dc level signal in an amplifier operated from a single power supply is given in Fig. 7.

Fig.7. The final block scheme of the biased amplifier

#### **III. METHOD ILLUSTRATIONS**

#### A. Non-inverting amplifier

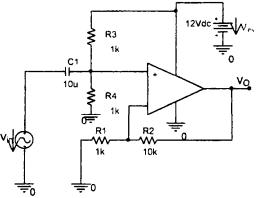

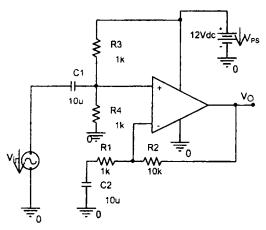

The circuit with the VTC presented in Fig.1 corresponds to a non-inverting amplifier that looks like the one in Fig. 8. To be able to use this circuit to amplify the  $v_1$  voltage we apply all the steps presented in the previous paragraph.

Fig.8. The non-inverting amplifier

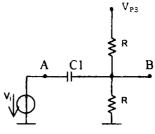

First we translate the VTC using the  $V_{BIAS}$  voltage series connected at the input of the amplifier. The  $V_{BIAS}$  voltage is obtained through the voltage divider from the power supply voltage  $V_{PS}$ . The series connection is realized by the C<sub>1</sub> capacitor, resulting the intermediary circuit depicted in Fig. 9.

Fig 9. The non-inverting amplifier after connecting the bias voltage

To "roll off" the gain to unity at dc, we introduce another  $C_2$  capacitor on negative feedback (Fig. 10).

Fig. 10. The final circuit for non-inverting amplifier

The equivalent circuit that shows how the  $V_{BIAS}$  voltage appears in the circuit is the one in Fig. 11. The equivalence is made for the steady state regime, where

Fig.11. The equivalent circuit for non-inverting amplifiers

The equations in the circuit are:

$$v_O = (v_{in} + V_{BIAS})(1 + \frac{R_2}{R_1}) - \frac{R_2}{R_1} V_{BIAS}$$

(10)

$$v_0 = v_{in} \cdot A_v + V_{BIAS} \tag{11}$$

$$A_{\nu} = 1 + \frac{R_2}{R_1}$$

(12)

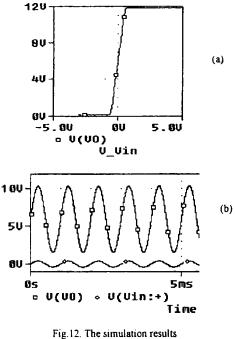

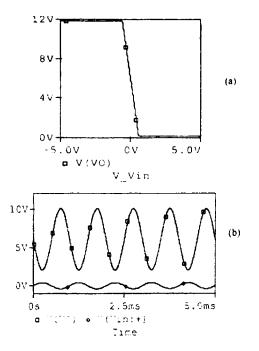

The VTC and the waveforms of the input voltage with  $z_{ro} = c_{l-1} + c_{in}$ , and  $t_{ro} = c_{o}(1) + c_{o}(1) + c_{o}(1)$  and the simulation are presented in Fig. 12.

(a) VTC; (b) waveforms

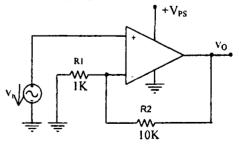

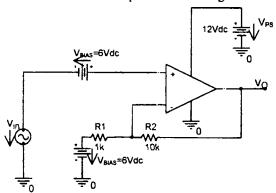

## B. Inverting amplifier

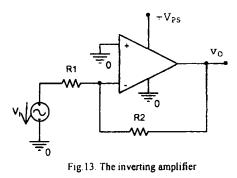

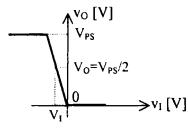

In Fig. 13 is presented the circuit and in Fig. 14 the VTC of an inverting amplifier.

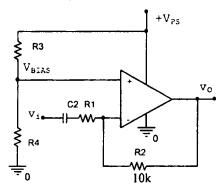

A consistent with  $V_{BIAS}$ . Unlike the non-inverting amplifier, in this case only the C<sub>2</sub> capacitor is necessary on the negative feedback

Fig.14. The V<sub>C</sub> of the inverting amplifier

path of the amplifier, because the input is applied at the non-inverting input of the op-amp. The capacitor realized both the series connection of the  $V_{BIAS}$  with input voltage and the unitary dc gain. The final circuit is the one in the Fig. 15.

Fig.15. The final circuit for inverting amplifier

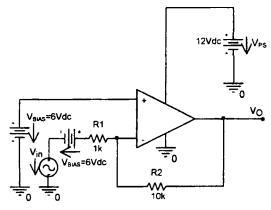

The equivalent circuit that shows how the  $V_{BIAS}$  voltage appears in the circuit is the one in Fig.16. The equivalence is made for the steady state regime, where the capacitor can be replaced with a d.c. voltage source and also the voltage divider can be replaced with a d.c. voltage source.

Fig.16. The equivalent circuit for inverting amplifier

The equation of the amplifier is:

$$v_O = -(v_{in} + V_{BIAS})\frac{R_2}{R_1} + (1 + \frac{R_2}{R_1})V_{BIAS}$$

(13)

$$v_{O} = -v_{in} \frac{R_2}{R_1} + V_{B/AS}$$

(14)

$$A_{v} = -\frac{R_{2}}{R_{1}}$$

(15)

The simulation results are presented in Fig. 17: the VTC in Fig 17.(a) and the waveform of the input voltage  $v_0(t)$  and the final voltage  $v_0(t)$  in Fig 17.(b). The simulation results showed that our method is correct.

Fig.17. The simulation results for inverting amplifier (a) VTC; (b) waveforms

## **IV. CONCLUSIONS**

We presented an intuitive method to deal with the amplification of a zero d.c. level variable signal using an op-amp operated from a signal p<sup>+</sup>w<sup>-</sup> u<sup>--</sup>ly. The examples presented here (for a non-inverting and for an inverting op-amp amplifier) demonstrates the use-lness of the method, especially for the struggle" with electronics. This method can save classroom instruction dimension h lp the surdents to understand and easily solve this kind of problem.

This method can be further use to try new way to bias some amplifiers in a desired operating point, even transistor amplifiers.

#### REFERENCES

Sedra, A.S., Smith, K.C., Microelectronic Circuits, Holt, Rinehart and Winston, Inc, 1987

Oltean, G., Dispozitive si circuite electronice. Dispozitive electronice, Risoprint, Cluj-Napoca, 2003

Horowitz, P, Hill, W., The Art of Electronics, Cambridge University Press, 1997

[4]. Oltean, G., Gordan, Mihaela, Oltean, Ioana, A new method to deduce the voltage transfer characteristic for some two-port network, Acta Tehnica Napocensis Electronics and Telecommunications, Vol. 40, Nr. 2, 2000, pp 17-20.