# Contribuții la îmbunătățirea dependabilității si securității informației

Teza de doctorat

Rodica Tirtea

Coordonator științific: prof. dr. ing. Mircea Vlăduțiu Universitatea Politehnica Timișoara

Președinte: Prof. dr. ing. Proștean Octavian Conducător de doctorat: Prof. dr. ing. Vlăduțiu Mircea Membrii:

- 1. Prof. dr. ing. Petrescu Mircea, Universitatea "Politehnica" din București

- 2. Prof. dr. ing. Deconinck Geert, Universitatea Catolica Leuven din Belgia

- 3. Prof. dr. ing. Mang Ioan, Universitatea din Oradea.

## Dependability and information security enhancements

Ph.D. thesis Rodica Ţirtea

# CUVÂNT ÎNAINTE

Această teza de doctorat a fost elaborată sub coordonarea d-lui profesor dr. ing. Mircea Vlăduţiu din cadrul Universităţii "Politehnica" din Timişoara. Doresc să-i mulţumesc şi pe această cale conducătorului de doctorat, prof. dr. ing. Mircea Vlăduţiu, pentru sugestiile şi încurajările deosebit de utile în munca de cercetare dar si pentru promptitudinea cu care a răspuns întotdeauna. Pe parcursul anilor care au trecut de când m-am înscris la doctorat, deşi o buna perioadă mi-am desfăşurat activitatea de studiu si cercetare în străinătate, discuţiile profesionale, coordonarea şi îndrumarea nu s-au diminuat.

Doresc de asemenea să mulţumesc membrilor comisiei de doctorat, referenţilor, pentru că au acceptat sa facă parte din comisia de doctorat. Le mulţumesc d-lui academician prof. dr. ing. Mircea Petrescu, d-lui prof. dr. ing. Ioan Mang de la Universitatea din Oradea şi nu în ultimul rând d-lui prof. dr. ing. Geert Deconinck căruia ţin sa-i mulţumesc şi pe această cale pentru colaborarea foarte bune pe care am avut-o pe durata studiilor mele de doctorat în K.U.Leuven, Belgia.

Aș dori de asemenea să mulţumesc membrilor colectivului din Catedra de Calculatoare a Facultății de Automatică și Calculatoare a Universității "Politehnica" din Timișoara pentru sugestiile utile pe care le-au exprimat cu ocazia susținerii examenelor sau referatelor.

Le mulţumesc de asemenea profesorilor mei din Universitatea din Oradea, colegilor din Catedra de Calculatoare, pentru îndrumare şi sprijin.

Aceasta teză nu ar fi fost posibilă fără susţinerea permanentă şi necondiţionată a părinţilor mei. Le mulţumesc şi pe această cale pentru răbdarea de care au dat dovadă în toţi aceşti ani dedicaţi studiului.

Oradea, ianuarie 2007

Rodica Tirtea

Părinților mei.

Tirtea, Rodica Contribuții la îmbunătățirea dependabilității si securității informației Teze de doctorat ale UPT, Seria 1, Nr. 23, Editura Politehnica, 2006, 104 pagini, 33 figuri, 17 tabele. ISSN:1224-6069 Cuvinte cheie: dependabilitate, toleranta la defecte, securitatea informatiei, algoritmi criptografici Rezumat, Conform ultimelor cercetări conceptele de dependabilitate și securitate nu mai pot fi separate chiar dacă până recent s-au dezvoltat independent. Aceasta lucrare adresează nevoia de securitate în sistemele cu cerințe de dependabilitate, și în același timp, nevoia de dependabilitate a mecanismelor de securitate implementate. Dependențele dintre securitate și dependabilitate sunt identificate și sunt introduse contribuții în domeniul implementărilor criptografice tolerante la defecte. Toleranța la defecte este necesară în implementările criptografice pentru a preveni noile tipuri de atacuri și vulnerabilități (atacuri bazate pe analiza erorilor). Data fiind gama largă de algoritmi criptografici, în această lucrare este analizat cazul cifrurilor bloc (algoritmi care asigură confidențialitatea). In această lucrare tehnici noi de detectare a erorilor sunt propuse, analizate și evaluate pentru cifruri bloc. Rezultatele obținute în urma simulărilor hardware sunt comparate cu cele ale cercetărilor anterioare. Aceasta lucrare aduce noi argumente care susțin dependența dintre dependabilitate și securitate și contribuie, cu tehnici noi, avantajoase din punct de vedere al costului, la asigurarea dependabilității implementărilor criptografice.

## **TABLE OF CONTENT**

| Cuvânt înainte                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Table of content                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                |

| List of figures                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                |

| List of tables                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                |

| List of abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                               |

| Rezumat                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                               |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12                               |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                               |

| 1.1. Context of the work<br>1.2. Contributions<br>1.3. Thesis structure                                                                                                                                                                                                                                                                                                                                                                  | 14                               |

| 2. On the need for security in dependable systems                                                                                                                                                                                                                                                                                                                                                                                        | 16                               |

| <ul> <li>2.1. Terminology</li> <li>2.1.1. Basic concepts</li> <li>2.1.2. Dependability, security and their attributes</li> <li>2.1.3. Cryptography and cryptanalysis</li> <li>2.1.4. Systems and their characteristics</li> <li>2.2. Security as requirement for dependable systems</li> <li>2.3. Intrusion tolerance approaches. Using fault tolerance to address security issues</li> <li>2.4. Contributions and conclusions</li></ul> | 16<br>17<br>19<br>24<br>25<br>27 |

| 3. Security – means, trends, challenges                                                                                                                                                                                                                                                                                                                                                                                                  | 30                               |

| <ul> <li>3.1. State-of-the-art in cryptography. Competitions and selected algorithms</li></ul>                                                                                                                                                                                                                                                                                                                                           | 30<br>33<br>36                   |

| 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| ē   | B.2. Cryptanalysis. Attacks based on implementation. Fault analysis         attacks       39         3.2.1. Cryptosystems and side-channel attacks       40         3.2.2. Fault attacks. Fault injection methods       41         3.2.3. Fault analysis attack       42         3.3. Standards       42         3.4. Conclusions and contributions       44                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0<br>1<br>2<br><i>3</i>         |

| 4.  | Modes of operation and their security in case of faults46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                               |

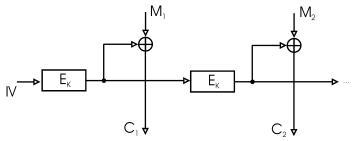

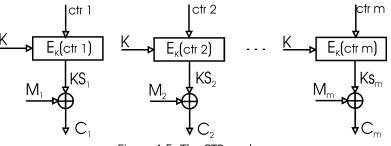

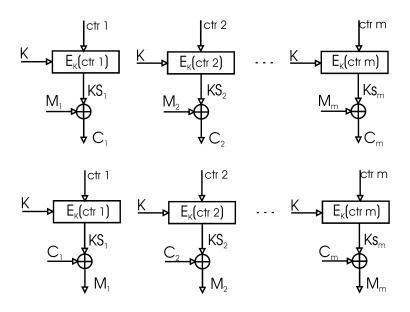

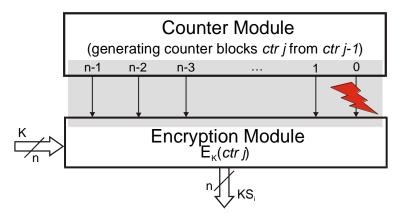

|     | 4.1. Modes of operation       46         4.1.1. ECB (Electronic Code Book) mode       47         4.1.2. CBC (Cipher Block Chaining) mode       47         4.1.3. CFB (Cipher FeedBack) mode       48         4.1.4. OFB (Output FeedBack) mode       48         4.1.5. CTR (Counter) mode       49         4.2. Modes of operation and bit errors       51         4.3. Counter Mode standardized implementations       52         4.3.1. Standard Incrementing Function in NIST Recommendations       52         4.3.2. Counter Mode and IPsec       54         4.3.3. Counter Mode in ATM Security Specifications       55         4.4. Faults and their impact on security in case of Counter Mode       56         4.5. How to avoid vulnerabilities for the modes of operation       58 | 778991234568                    |

| 5.  | Fault tolerance for secure implementations of block ciphers60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                               |

| Ĩ   | 5.1. Available mechanisms protecting block ciphers against fault analysis         attacks       60         5.1.1. Fault analysis attacks for block ciphers       60         5.1.2. Error detection mechanisms for block ciphers       61         5.2. Case study. Triple-DES       62         5.2.1. Short presentation of Triple-DES       62         5.2.2. Applying error detection methods for Triple-DES algorithm       63         5.2.3. Fault analysis attack resistant key scheduling algorithm for       64         5.2.4. Using complementation property for fault tolerance purposes       64         5.3. Conclusions and contributions       70                                                                                                                                | 0<br>0<br>1<br>2<br>3<br>8<br>8 |

| 6.  | Cost analysis of error detection techniques for MISTY1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| cry | ptographic algorithm72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                               |

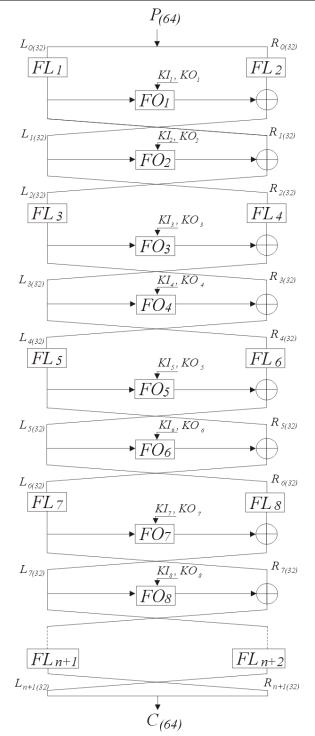

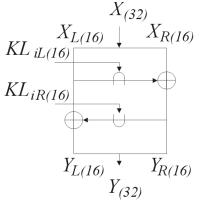

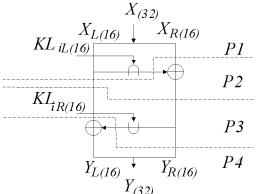

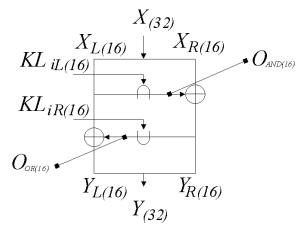

|     | 5.1. MISTY1 algorithm       72         6.1.1. Why MISTY1 algorithm?       73         6.1.2. Encryption with MISTY1       73         6.1.3. Considerations regarding the security analysis of MISTY1       78         5.2. Hardware simulation environment       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>3<br>8                     |

6

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

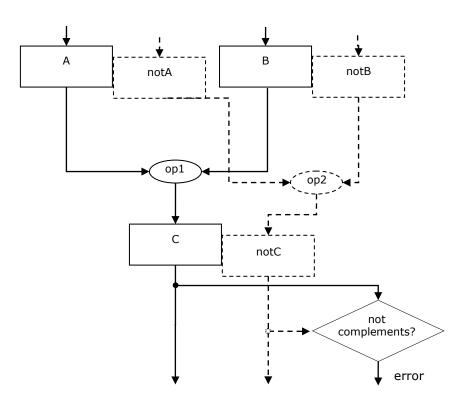

| 6.3. Error propagation in MISTY1 algorithm816.4. MISTY1 and the available error detection techniques836.5. Complemented duplication error detection846.5.1. Error detection using complemented duplication846.5.2. Description of CD error detection using Boolean algebra856.5.3. Applying CD error detection for MISTY1 functions866.5.4. Analysis of overhead costs886.6. Using parity prediction for error detection896.7. Analysis of overhead in related work. Comparison916.8. Conclusions92 |

| 7. Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1. Findings of this dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Annex A. Misty1 algorithm, S-boxes97                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# LIST OF FIGURES

| 40<br>Figure 4.1. Electronic Code Book mode                                                                          |

|----------------------------------------------------------------------------------------------------------------------|

| Figure 4.3. Cipher Feedback mode48Figure 4.4. Output Feedback mode49Figure 4.5. The CTR mode50                       |

| Figure 4.5. The CTR mode                                                                                             |

| Figure 4.9. ATM state vector fields                                                                                  |

| Figure 4.10. Fault on the LSB of the Counter module output (n =the size of the encryption/decryption block)          |

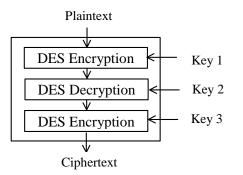

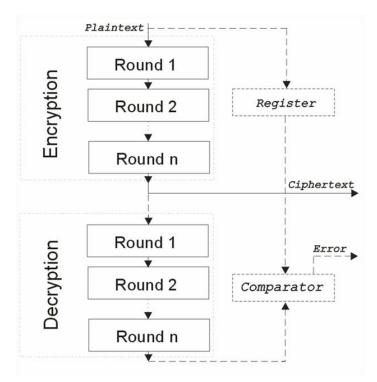

| Figure 5.1. Triple-DES - general architecture.63Figure 5.2. Algorithm level error detection. General view.64         |

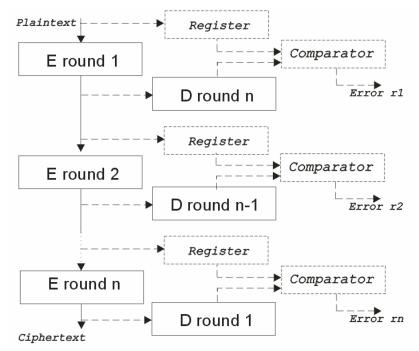

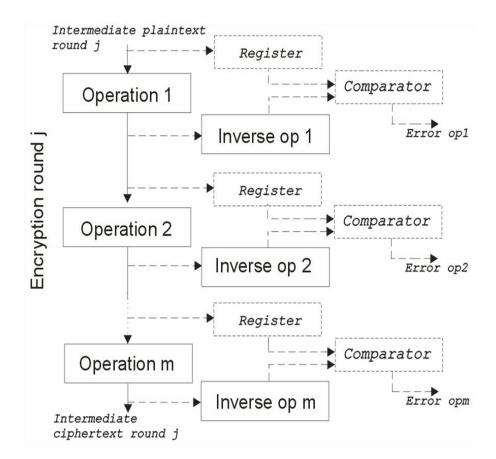

| Figure 5.3. Round level error detection. General view.65Figure 5.4. Operation level error detection. General view.67 |

| Figure 5.5. Error detection mechanism for Triple-DES relying on complementation property                             |

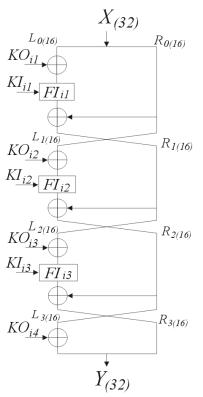

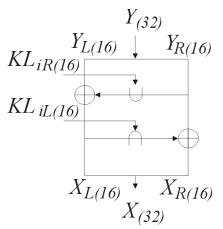

| Figure 6.1. Encryption procedure for MISTY1                                                                          |

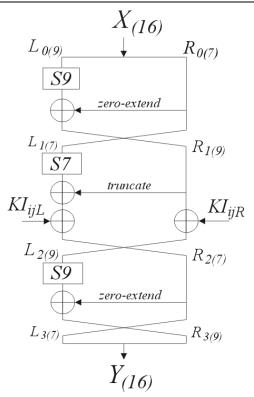

| Figure 6.4. Function FI                                                                                              |

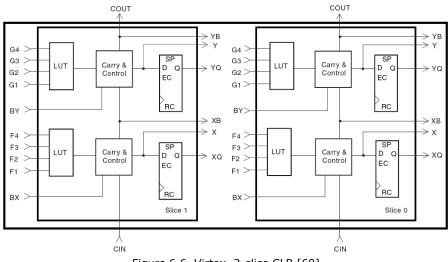

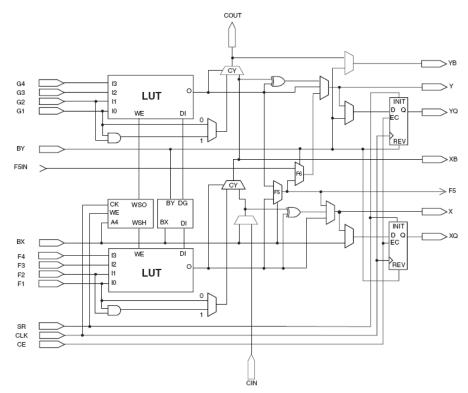

| Figure 6.6. Virtex. 2-slice CLB [60]                                                                                 |

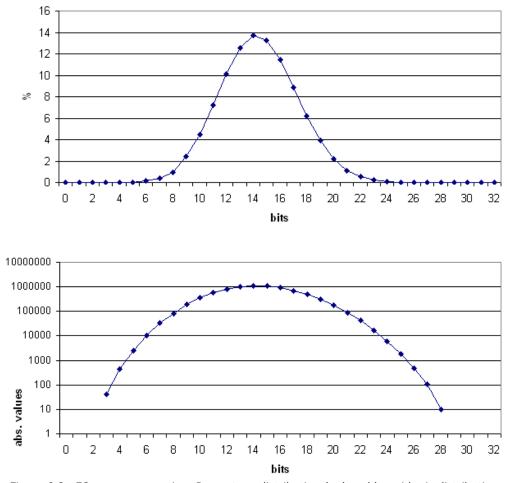

| distribution (down)                                                                                                  |

# LIST OF TABLES

| 21    |

|-------|

| 31    |

| 31    |

| 31    |

| 32    |

| 32    |

| 36    |

| 37    |

| 38    |

| 66    |

| -DES  |

| 69    |

| 78    |

| 86    |

| 87    |

| 87    |

| 88    |

| 89    |

| of FL |

| 91    |

|       |

## LIST OF ABBREVIATIONS

| 3GPP     | 3rd Generation Partnership Project                                 |

|----------|--------------------------------------------------------------------|

| AES      | Advanced Encryption Standard                                       |

| ATM      | Asynchronous Transfer Mode                                         |

| CBC      | Cipher Block Chaining                                              |

| CD       | Complemented Duplication error detection                           |

| CED      | Concurrent Error Detection                                         |

| CFB      | Cipher FeedBack                                                    |

| CRYPTREC | CRYPTography Research and Evaluation Committees                    |

| CTR      | Counter Mode                                                       |

| DES      | Data Encryption Standard                                           |

| DFA      | Differential Fault Analysis                                        |

| ECB      | Electronic Code Block                                              |

| FIPS     | Federal Information Processing Standards                           |

| FPGA     | Field-Programmable Gate Array                                      |

| GSM      | Global System for Mobile Communications                            |

| IETF     | Internet Engineering Task Force                                    |

| IPsec    | Internet Protocol security                                         |

| ISO      | International Organization for Standards                           |

| ITUA     | Intrusion Tolerance by Unpredictable Adaptation                    |

| LFSR     | Linear Feedback Shift Register                                     |

| LUTs     | Look-Up Tables                                                     |

| MAC      | Message Authentication Code                                        |

| MAFTIA   | Malicious and Accidental Fault Tolerance for Internet Applications |

| NDFA     | Non-Differential Fault Analysis                                    |

| NESSIE   | New European Schemes for Signature, Integrity and Encryption       |

| NIST     | National Institute of Standards and Technology                     |

| OFB      | Output FeedBack                                                    |

| TLS      | Transport Layer Security                                           |

### REZUMAT

Dezvoltarea tehnologiei informației, a sistemelor de calcul și a aplicațiilor lor, au determinat și continuă să determine expansiunea unor domenii cu o istorie lungă. *Securitatea informației*, mii de ani utilizată pentru secretizarea comunicațiilor din domeniul militar sau diplomatic, este influențată astăzi de evoluția tehnologiei informației. Proliferarea calculatoarelor și a informației in format digital determină dezvoltarea unor tehnici și concepte noi care sa răspundă cerințelor cunoscute și utilizate de secole (concepte cum ar fi semnătura digitală, autentificarea sursei, etc. sunt dezvoltate pentru a extinde conceputul clasic de semnătura de pe pergament sau hârtie). Mai mult, dată fiind tendința spre o societate informatizată, alte domenii, cum ar fi telecomunicațiile civile, domeniul medical, etc. au nevoie de astfel de tehnici.

Un factor important în dezvoltarea și extinderea aplicațiilor care beneficiază de tehnologia informației este încrederea. Pentru a dezvolta sisteme sigure și fiabile în care sa putem avea justificat încredere este nevoie ca aceste sisteme sa răspundă cerințelor de *dependabilitate* si *securitate*. Altfel, ignorând aceste cerințe, consecințele pot fi grave (pierderi materiale și umane etc.) periclitând inclusiv încrederea societății în noile tehnologii.

Conform ultimelor cercetări, conceptele de dependabilitate și securitate nu mai pot fi separate, chiar dacă până recent s-au dezvoltat independent. Securitatea informației, prin câteva din obiectivele ei (integritatea datelor, autentificarea părților sau mesajelor etc.) aparține conceptului de dependabilitate, în timp ce conceptul de securitate utilizează mijloacele dependabilității (toleranta la defecte, prognosticarea defectelor) pentru a combate defectele intenționate și vulnerabilitățile. Având în vedere acest context, această lucrarea se concentrează pe dependența care există între dependabilitate, și securitate.

Aceasta teza adresează nevoia de securitate în sistemele cu cerințe de dependabilitate, și în același timp, nevoia de dependabilitate a mecanismelor de securitate implementate. Deoarece aceste domenii continuă să se extindă, sunt incluse analize ale stadiului actual de dezvoltare. Dependențele dintre securitate și dependabilitate sunt identificate și sunt introduse contribuții în domeniul implementărilor criptografice tolerante la defecte. Toleranța la defecte este necesară în implementările criptografice pentru a preveni noile tipuri de atacuri și vulnerabilități (atacuri bazate pe analiza erorilor). Data fiind gama largă de algoritmi criptografici, în această lucrare este analizat cazul cifrurile bloc (algoritmi care asigură confidențialitatea). In această lucrare tehnici noi de detectare a erorilor sunt propuse, analizate și evaluate pentru cifruri bloc. Rezultatele obținute în urma simulărilor hardware sunt comparate cu cele ale cercetărilor anterioare. Aceasta lucrare aduce noi argumente care susțin dependența dintre dependabilității implementărilor criptografice.

### ABSTRACT

Since long, advances in computer technologies and networks determine developments in other fields. *Information security*, with its roots thousands of years ago in the need for secrecy associated to diplomacy and military, benefits nowadays from these advances. The widespread use of computers and information in digital form, demands new techniques and concepts, equivalent to long time known and used ones (e.g. digital signature, non-repudiation, data origin authentication are information security objectives relying on signature concept). Nevertheless, not only diplomacy and military are using information security today - security products are developed and deployed to answer security needs in other public services in an information intensive society (e.g. telecommunications, banking, health care).

However, trust is an important factor in deployment of new technologies and services in general and computer technologies in particular in an information society. Without consideration of *dependability* and *security* aspects in the design and development of new products, severe consequences may occur (accidents, security attacks etc.), besides jeopardizing public trust. Dependability and security through their means and objectives supply methods and techniques to develop systems and deliver services in which we can justifiably trust.

Recent research advocates that security and dependability cannot be separated anymore, even if the two fields developed separately. Information security through its objectives (data integrity, entity and message authentication, etc.) is part of the dependability concept, while security uses dependability means (e.g. fault tolerance, fault forecasting) to address malicious faults. Starting from this context, this work addresses the dependencies between security and dependability.

This work covers both security and dependability fields concentrating on the need for security in dependable systems and on the need for dependability of security mechanisms implementations. Due to extensive research and permanent evolution in the fields, state-of-the-art surveys are included. The dependencies between security and dependability are identified and contributions are introduced in the topic of fault-tolerant cryptographic implementations. Fault tolerance is required in security implementations to overcome the new types of vulnerabilities and attacks (e.g. fault analysis attacks). Given the wide area of cryptographic primitives, this work focuses on confidentiality algorithms, specifically block ciphers. New error detection techniques are proposed, applied and evaluated in this thesis for block ciphers. The results of hardware implementations and simulations are compared with the ones of previous proposed solutions. The findings of this work bring new arguments supporting the dependencies between security and dependability and contribute with new, low cost techniques for dependable security implementations.

## **1. INTRODUCTION**

#### **1.1. Context of the work**

Critical and non-critical applications rely increasingly on information technologies for their operation. From telephony, or on-board computers, navigation systems and other technologies in today's automobiles to control systems in power plants or flight systems, information technology is part of our lives more and more every day. The introduction of information technology, especially for general public relies on the *trust* that the delivered services meet requirements for safety, reliability, etc. Trust is defined as the *expectation* that a service will be provided or a commitment will be fulfilled [1]. The engineering aspects related to trust are covering issues such as dependability and security.

The *dependability* of information technologies has to be address to secure correct and continuous services delivery. *Dependability* is that property of a computer system such that reliance can justifiably be placed on the service it delivers [2].

Besides the requirements for dependability of the systems/applications using information technologies, the requirements for *security* have to be addressed. The market pressure to deploy low cost solutions, the move from centralized to distributed solutions and from wired to wireless connectivity generate new type of challenges in order to meet increasingly stringent privacy and security requirements. *Information security* has as objectives, between others, privacy or confidentiality, entity and data authentication, data integrity, non-repudiation [3].

Security is progressively more needed in different fields. Computing applications deployed for instance in financial systems or health care systems have to address by default requirements for confidentiality, data and entity authentication, data integrity, non-repudiation, etc. in order to deliver their services. However, nowadays, other applications relying on distributed systems, for instance deployed in infrastructures (e.g. electric power infrastructure), take advantage of the widespread use of Internet and mobile communications to deliver their services [4]. In this case the communication between different components of the applications/systems has to address the challenges of a public environment which can become hostile (e.g. malicious attempts to jeopardize the security of the services can be encountered). From these examples can be noticed that security is needed not only in the fields where traditionally secrecy was required, but also in other fields where dependability and survivability of services are mandatory. As such security is indispensable in order to deliver dependable services.

The two concepts, dependability and security, are used together lately [5] to express requirements for reliable, available, safe, secure etc. services delivered by computing systems. We illustrated that security is used to deliver dependable services. Nevertheless, dependability is needed to assure correct, fault-free security implementations. Hence the requirements for dependability and security cannot be separated anymore.

In this work the focus is on security as a means to address dependability requirements. This objective is achieved by identifying vulnerabilities and proposing

solutions to diminish the impact of malicious attempts on the dependability of computing systems. Furthermore, because dependable systems rely on security techniques (e.g. implemented algorithms) the reliability of cryptographic implementations is another issue addressed in this thesis. Hence the dependencies between dependability and security are covered in this work. However this work has no pretension to cover all aspects of these dependencies.

#### **1.2.** Contributions

This thesis addresses the relationship between dependability and security, and motivates the need for security in dependable systems. However, cryptographic means (e.g. algorithms, protocols) are used to implement security systems. As such, these implementations need to be reliable. Thus the reliability of cryptographic systems facing new type of implementation related attacks is addressed. Starting from the state-of-the-art research on security and dependability, in this work both theoretical and practical contributions are introduced. A list of the contributions follows:

- state-of-the-art investigation of

- security and cryptographic algorithms,

- intrusion tolerance approaches,

- mechanisms to detect/tolerate errors in cryptographic implementations;

- focusing errors and their impact on cryptographic systems

- identifying vulnerabilities for operation modes;

- proposing solutions to avoid vulnerabilities in operations modes;

- proposing and applying new error detection techniques for cryptographic implementations;

- cost analysis of new error detection techniques and suitability analysis of these new error detection techniques to other algorithms;

- implementation of a new low-cost error detection mechanism for a cryptographic algorithm;

- comparison of/with related work results.

#### **1.3. Thesis structure**

This work has the following structure:

**Chapter 2** introduces the need for security in dependable systems. After a terminology section, the current trends in infrastructures relying on information systems are analyzed. In this chapter we show that the need for security is not only justified by the classical requirements i.e. for confidentiality of certain transferred data, but also by the need for correct/normal functionality/operation, e.g. allowing protection in case of malicious faults (e.g. intrusion attempts).

In **Chapter 3** security is addressed. An up-to-date state-of-the-art investigation of cryptographic techniques and cryptanalysis is presented. Related work on intrusion tolerance is introduced. The challenges given by new type of attacks from the category of side-channel attacks (e.g. fault analysis attacks) are summarized.

**Chapter 4** is focused on security and its need for fault tolerance. Fault tolerance is a dependability means needed in security implementation not only for

correct operation but also for protection against fault analysis attack. Security analysis of a new operation mode is included. Vulnerabilities are identified for different standardized recommendations (e.g. IPsec) and solutions are proposed to avoid such vulnerabilities.

In **Chapter 5** error detection and tolerance mechanisms designed to protect cryptographic implementation against fault analysis attacks are presented. Security analysis of a new proposed error detection mechanism is included and also a case study regarding cost analysis and applicability of available fault tolerance mechanisms for the Triple-DES algorithm. Properties of cryptographic algorithms (e.g. complementation property) are analyzed in order to build new error detection mechanisms. Cost analysis is provided for the new error detection mechanism relying on complementation property.

**Chapter 6** contains evaluation and cost analysis of a new error detection mechanism, using complemented duplication, applied for Misty1 algorithm. The implementations costs are compared with the results of other methods, and the comparison shows that our method has a low hardware and time overhead. Besides the low cost implementation, this detection technique is more secure than other techniques from related work. A clear distinction is made between theoretical assumptions of cost of implementation and the implementation/simulation results reported by simulation tools, where optimization is used. The related work is criticized and we show that in case of implementation using FPGA the reported values are not always in range with the theoretical assumption – due to the composition of the logical units used in the FPGA and due to the mapping process.

In **Chapter 7** conclusions are summarized and future work is proposed.

### 2. ON THE NEED FOR SECURITY IN DEPENDABLE SYSTEMS

Information technologies deployed in various fields, where dependability and survivability are required, rely on security techniques. This reliance on security is justified for instance by traditional requirements for confidentiality and secrecy (e.g. in finance) and by requirements for authentication, integrity, etc. due to the environment in which the underlying system is integrated (e.g. the way the connectivity is assured, for instance using Internet). In this chapter, after introducing the terminology, the problems addressed in this work are presented together with the solutions proposed such that the requirements for security in dependable systems are fulfilled.

#### 2.1. Terminology

#### 2.1.1. Basic concepts

A **system** is an entity that interacts with other entities, i.e., other systems, including hardware, software, humans, and the physical world with its natural phenomena. Those other systems are the **environment** of the given system [5].

Computing and communication systems are characterized by *functionality*, *performance*, *dependability*, and *cost*. Other system properties are *usability*, *manageability* and *adaptability*. The **function** of a system is what the system is intended to do and is described by *functional specifications*. The **behavior** of a system is what the system does to implement its function, and is described by a sequence of *states*. The **service** delivered by a system, in its role as **provider**, is its behavior as it is perceived by its user(s); a **user** is another system that receives services from the provider [5]. **Correct service** is delivered when the service implements the system function. A **service failure** is an event that occurs when the delivered service deviates from correct service [5]. The period of delivery of incorrect service is a **service outage**.

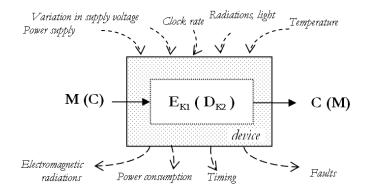

A deviation from correct state is called an **error**. The adjudged or hypothesized cause of error is called **fault**. Faults can be internal or external to a system. The prior presence of a **vulnerability**, i.e., an internal fault that enables an external fault to harm the system, is necessary for an external fault to cause an error an possible subsequent failure(s). A fault is **active** when it causes an error, otherwise it is **dormant**. The manifestation mechanisms of faults, errors and failures are presented in figure 2.1.

$\cdots$  fault  $\xrightarrow{activation}$  error  $\xrightarrow{propagation}$  failure  $\xrightarrow{causation}$  fault  $\rightarrow \cdots$

#### Figure 2.1. Chain of threats [5]

When more services are delivered by a system, the failure of one or more of the services may leave the system in a degraded mode, still offering a subset of the needed services to the user (e.g. slow service). In this context it can be said that the system suffered a partial failure of its functionality or performance.

#### 2.1.2. Dependability, security and their attributes

**Dependability** is that property of a computer system such that reliance can justifiably be placed on the service it delivers [2]. The term dependability is used to encapsulate the concepts of reliability, availability, safety, maintainability, performability, and testability according to [6], while [5] includes also integrity and confidentiality.

The **reliability** of a system is a function of time, R(t), defined as the conditional probability that the system performs correctly throughout the interval of time,  $[t_0, t]$ , given that the system was performing correctly at time  $t_0$ .

**Availability** is a function of time, A(t), defined as the probability that a system is operating correctly and is available to perform its functions at the instance of time, t.

**Safety** is the probability, S(t), that a system will either perform its functions correctly or will discontinue its functions in a manner that does not disrupt the operation of other systems or compromise the safety of any people associated with the system. Safety is a measure of the **fail-safe** capability of a system [6].

The **performability** of a system is a function of time, P(L,t), defined as the probability that the system performance will be at, or above, some level, L, at the instance of time, t. **Graceful degradation** is the attribute of a system to automatically decrease its level of performance to compensate for hardware or software faults, allowing performance at some reduced level [6]. **Robustness** characterizes a system's dependability with respect to external faults.

**Maintainability** is the probability, M(t), that a failed system will be restored to an operational state within a period of time t.

**Testability** is the ability to test for certain attributes within a system [6].

**Integrity** is defined as the absence of improper system alteration.

Consideration of other type of faults, such as intentional malicious and nonmalicious faults, justified the introduction of integrity as an attribute for dependability, and, in the same time bringing together dependability and security to characterize systems.

**Security** encapsulates attributes of *availability, confidentiality* and *integrity* requiring the concurrent existence of 1) availability for authorized actions only, 2) confidentiality, and 3) integrity, as already defined, but with "improper" meaning "unauthorized" [5]. **Confidentiality** is the absence of unauthorized disclosure of information; is a service used to keep the content of information from all but those authorized to have it. **Non-repudiation** prevents an entity from denying previous commitments or actions [3]. **Authentication** is related to identification and is applied to both entities and information: *entity authentication* and *data origin authentication*. Data origin authentication implicitly provides data integrity (if a message is modified, the source has changed). **Authorization** is defined as a conveyance, to another entity, of official sanction to do or be something [3].

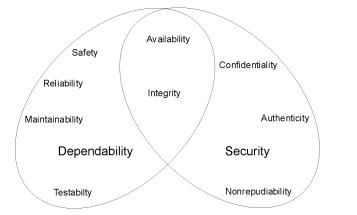

In figure 2.2 the relationship between dependability and security is illustrated. As can be seen, *availability* (for authorized action) and *integrity* are common, while other attributes belong to one or the other concepts.

Figure 2.2. Dependability and security relationship

All security attributes mentioned in figure 2.2 are used according to the situation and requirements, so that all parties of a transaction must have confidence that certain objectives associated with information security are met. Besides confidentiality, integrity, entity or data authentication, authorization and non-repudiation other concepts are part of *information security* objectives [3] and some of them are listed below:

- signature - a means to bind information to an entity;

- validation – a means to provide timeliness of authorization to use or manipulate information or resources;

- access control - restriction access to resources to privileged entities;

mcertification – endorsement of information by a trusted entity;

- confirmation - acknowledgement that services have been provided;

anonymity – concealing the identity of an entity involved in some process;

- revocation – retraction of certification or authorization.

Security can be achieved through the information itself or through other physical means (e.g. physical documents recording it, for banknotes special material and ink are used to avoid counterfeiting). As lately an increased amount of information is managed in electronic form, information security relies on digital information itself. *Algorithms* and *protocols* have been developed to answer the objectives of information security. **Cryptography** supplies a set of *techniques* for information security. *Cryptography* is the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication, data origin authentication [3]. In section 2.1.3 further explanations are given for cryptography and other related topics.

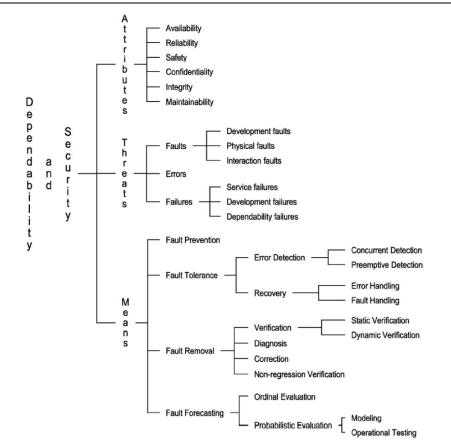

There are four major categories of *means* to attain *dependability and security* [5]: **fault prevention**, to prevent the occurrence or introduction of faults, **fault tolerance**, to avoid service failure in the presence of faults, **fault removal**, to reduce the number and severity of faults and **fault forecasting**, to estimate the present number, the future incidence, and the likely consequences of faults (figure 2.3).

**Survivability** is the ability to continue to provide services (even degraded e.g. supporting graceful degradation) in the case of fault or changes/events causing degradation of the system or of its operational environment.

#### 2.1.3. Cryptography and cryptanalysis

The art and science of keeping messages secure is **cryptography**, and it is the work of cryptographers. Cryptanalysts are practitioners of **cryptanalysis**, the art and science of *breaking ciphertext*; that is, seeing through the disguise. The branch of mathematics encompassing both cryptography and cryptanalysis is **cryptology** and its practitioners are cryptologists [7].

Cryptography provides a set of techniques to support the four major objectives of the information security: confidentiality, data integrity, authentication and non-repudiation. *Cryptographic tools*, also called *primitives* are used to provide information security [3]. Primitives have been designed to answer the need for confidentiality (e.g. encryption schemes), authentication (e.g. digital signature schemes), etc.

#### 2.1.3.1. Encryption and decryption

One of the purposes of *cryptography*, especially for confidentiality, is to protect transmitted information from being read and understood by anyone except the intended recipient. **Encryption** means the conversion of the original message (plaintext) to encrypted text (ciphertext). The reverse process (conversion of chipertext in plaintext) is called **decryption**.

Usually the following notation is used. M denotes plaintext for message, or P, for plaintext. Ciphertext is denoted by C. The encryption function E, operates on M to produce C:

$$E(M) = C$$

(2.1)

In the reverse process, the decryption function D operates on C to produce

$$D(C) = M$$

(2.2)

Since the whole point of encrypting and then decrypting a message is to recover the original plaintext, the following identity must hold true:

$$D(E(M)) = M$$

(2.3)

A **cryptographic algorithm**, also called a **cipher**, is the mathematical function used for encryption and decryption. (Generally, there are two related functions: one for encryption and the other for decryption.)

If the security of an algorithm is based on keeping the way that algorithm works a secret, it is a *restricted* algorithm. Restricted algorithms are inadequate by today's standards. If someone accidentally reveals the secret, everyone must change their algorithm.

Modern cryptography solves this problem with a **key**, denoted by K. The key might be any one of a large number of values. The range of possible values of the key is called the **key space**. Both the encryption and decryption operations use this key (i.e., they are dependent on the key), so the functions now become:

$$E_{K}(M) = C$$

(2.4)

$D_{K}(C) = M$  (2.5)

These functions have the property that:

$D_{K}(E_{K}(M)) = M$  (2.6)

Some algorithms use a different encryption key and decryption key. That is, the encryption key,  $K_1$ , is different from the corresponding decryption key,  $K_2$ . In this case:

$$E_{K1}(M) = C \qquad (2.7)$$

$$D_{K2}(C) = M \qquad (2.8)$$

$$D_{K2}(E_{K1}(M)) = M \qquad (2.9)$$

All of the security in these algorithms is based in the key (or keys); none is based in the details of the algorithm. This means that the algorithm can be published and analyzed. Products using the algorithm can be mass-produced. If an eavesdropper knows the algorithm he/she cannot read the messages as long as he/she does not have knowledge about the particular key.

There are two general types of key-based algorithms: **symmetric** and **public-key.**

*Symmetric algorithms*, sometimes called conventional algorithms, are algorithms where the encryption key can be calculated from the decryption key and vice versa. In most symmetric algorithms, the encryption key and the decryption

M:

key are the same. These algorithms, also called *secret-key algorithms* require that the sender and receiver agree on a key before they can communicate securely. The security of a symmetric algorithm rests in the key; divulging the key means that anyone could encrypt and decrypt messages. As long as the communication needs to remain secret, the key must remain secret.

Encryption and decryption with a symmetric algorithm are denoted as in equations (2.4) and (2.5) and the equation (2.6) holds for any key.

Symmetric algorithms can be divided into two categories:

Some operate on the plaintext, a single bit (or sometimes byte) at a time; these are called **stream algorithms** or **stream ciphers**.

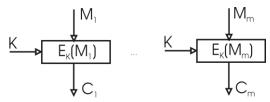

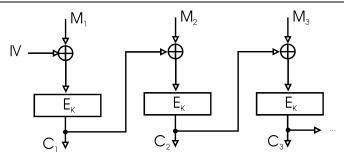

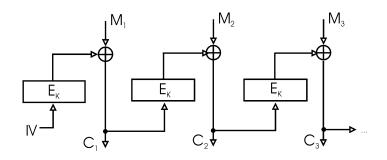

Others operate on the plaintext in groups of bits. The groups of bits are called **blocks**, and the algorithms are called **block algorithms** or **block ciphers** (the block size can be of 64 bits).

Symmetric block ciphers can be further described based on the techniques used for encryption e.g. **substitution ciphers**, **transposition ciphers**, **product ciphers**, **Feinstel ciphers** [3]. Substitution ciphers replace symbols (or groups of symbols) by other symbols or group of symbols. Transposition ciphers rely on permutation of symbols in a block. A product cipher combines two or more substitutions and/or transpositions in a manner intended to generate a more secure cipher. A **substitution-permutation network (SPN)** is a product cipher composed of a number of stages each involving substitutions and permutations.

**Iterated block ciphers** encrypt a plaintext block by a process that has several **rounds**. In each round, the same transformation (also known as a round function) is applied to the data using a **subkey**. The set of subkeys is usually derived from the user-provided secret key by a special function. The set of subkeys is called the **key schedule**. The number of rounds in an iterated cipher depends on the desired security level and the consequent trade-off with performance. In most cases, an increased number of rounds will improve the security offered by a block cipher, but for some ciphers the number of rounds required to achieve adequate security will be too large for the cipher to be practical or desirable [8].

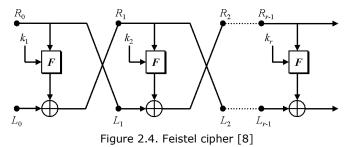

In a **Feistel cipher** (see Figure 2.4), the text is split into two halves ( $L_0$  and  $R_0$ ). The round function F is applied to one half using a subkey and the output of F is XORed with the other half. The two halves are then swapped. Each round follows the same pattern except for the last round where there is no swap. For Feistel ciphers encryption and decryption are structurally identical, though the subkeys used during encryption at each round are taken in reverse order during decryption (i.e. the input in the decryption algorithm is the pair ( $R_r$ ,  $L_r$ ) instead of the pair ( $L_0$ ,  $R_0$ ), and the i<sup>th</sup> subkey is  $k_{r-i+1}$ , not  $k_i$ . This means that we obtain ( $R_{r-i}$ ,  $L_{r-i}$ ) instead of ( $L_i$ ,  $R_i$ ) after the i<sup>th</sup> round.)

In case of block ciphers, for encryption/decryption the plaintext/ciphertext is

split into blocks. The way these blocks are manipulated during encryption/decryption is described by so called **modes of operation**. Several modes are also used for hiding existing patterns in the plaintext/ciphertext. Some of the standardized *modes of operation* are presented in Chapter 4.

*Public-key algorithms* (also called asymmetric algorithms) are designed so that the key used for encryption is different from the key used for decryption. Furthermore, the decryption key cannot (at least in any reasonable amount of time) be calculated from the encryption key. The algorithms are called *public-key* because the encryption key can be made public: a complete stranger can use the encryption key to encrypt a message, but only a specific person with the corresponding decryption key can decrypt the message. In these systems, the *encryption key* is often called the **public key**, and the *decryption key* is often called the **private key** (sometimes also called the secret key). Encryption using public key K<sub>1</sub> is denoted by as in equation (2.7), decryption using private key K<sub>2</sub> as in (2.8).

Sometimes, messages will be encrypted with the private key and decrypted with the public key; this is used in digital signatures.

A **cryptosystem** is an algorithm, plus all possible plaintexts, ciphertexts, and keys.

#### 2.1.3.2. Attacks

We are going to introduce shortly only the relevant attacks for this work. An attempted *cryptanalysis* is called an **attack**. A fundamental assumption in cryptanalysis is that the secrecy must reside entirely in the key [7]. It is assumed that the cryptanalyst has complete details of the cryptographic algorithm and implementation.

The standard technique for defeating a cryptosystem is known as the **brute force method/attack**. This assumes trying all the keys until a key is found which produces the plaintext message. Even if this method is simple and inglorious, brute force is still a form of cryptanalysis. However, using larger keys can make *brute force* a less than feasible technique. For example, a message encrypted with a 56-bit DES key could be broken within a few days of intense computing. A 128-bit key makes the cipher much more effective, ad there are algorithms using even larger keys e.g. RSA encryption commonly uses 512-bit keys. As a result, even with the increased computation power of the computers, better techniques for cryptanalysis are needed. Such a method (any which takes *less time or energy* than brute force) is termed a **break**.

The *parts of the cryptosystem* subjects for attacks are:

*The key*. Though the effectiveness of brute force is inversely proportional to the size of they key space, some ciphers have revealing characteristics which help find the proper key. These "hints" can dramatically reduce the key space that must be searched.

*The data*. Not only the keys, but also the ciphertext itself may have relevant and revealing information embedded within it (e.g. text pattern).

The algorithm. The strength of an algorithm is often based upon another problem that has been considered mathematically "difficult". If this characteristic problem can be solved more easily (than previously thought), the cipher may no longer be effective. For example, factoring large numbers is at the heart of RSA encryption. When factoring becomes more efficient than brute force, the cipher will be broken.

The *complexity* of an attack can be measured in different ways:

**Data complexity**. The amount of data needed as input to the attack.

**Processing complexity**. The time needed to perform the attack. This is often called the work factor.

**Storage requirements**. The amount of memory needed to do the attack.

The *complexity* of an attack is taken to be the minimum of these three factors. Some attacks involve trading off the three complexities: a faster attack might be possible at the expense of a greater storage requirement.

While the *complexity* of an attack is constant (until some cryptanalyst finds a better attack, of course), *computing power* is not. There have been phenomenal advances in computing power during the last half-century and there is no reason to think this trend is not going to continue. Many cryptanalytic attacks are perfect for parallel machines: the task can be broken down into billions of tiny pieces and none of the processors need to interact with each other. Pronouncing an algorithm secure simply because it is infeasible to break, given current technology, is hazardous. Good cryptosystems are designed to be infeasible to break with the computing power that is expected to evolve many years in the future [7].

There are numerous techniques for performing cryptanalysis, depending on what access the cryptanalyst has to the plaintext, ciphertext, or other aspects of the cryptosystem. Below are some of the *most common types of attacks*:

**Ciphertext-only attack**. A ciphertext-only attack is one in which the cryptanalyst obtains a sample of ciphertext, without the plaintext associated with it. This data is relatively easy to obtain in many scenarios, but a successful ciphertext-only attack is generally difficult, and requires a very large ciphertext sample;

**Known-plaintext analysis**. With this procedure, the cryptanalyst has knowledge of a portion of the plaintext from the ciphertext. Using this information, the cryptanalyst attempts to deduce the key used to produce the ciphertext. A *known-plaintext attack* is one in which the cryptanalyst obtains a sample of ciphertext and the corresponding plaintext as well;

**Chosen-plaintext analysis** (also known as **differential cryptanalysis**). There is often a statistical correlation between a key and the ciphertext which it produces. Understanding the specifics of this correlation and by using sufficient chosen plaintext can help find an unknown key. The cryptanalyst is able to have any plaintext encrypted with a key and obtain the resulting ciphertext, but the key itself cannot be analyzed. A chosen-plaintext attack is one in which the cryptanalyst is able to choose a quantity of plaintext and then obtain the corresponding encrypted ciphertext;

**Ciphertext-only analysis**. The cryptanalyst has no knowledge of the plaintext and must work only from the ciphertext. This requires accurate guesswork as to how a message could be worded. It helps to have some knowledge of the literary style of the ciphertext writer and/or the general subject matter.

**Man-in-the-middle attack**. This attack relies on tricking individuals into surrendering their keys. The cryptanalyst/attacker places him or herself in the communication channel between two parties who wish to exchange their keys for secure communication (via asymmetric or public key infrastructure cryptography). The cryptanalyst/attacker then performs a key exchange with each party, with the original parties believing they are exchanging keys with each other. The two parties then end up using keys that are known to the cryptanalyst/attacker. This type of attack can be defeated by the use of a hash function.

**Side-channel attacks.** The ciphers are implemented on many different platforms. Certain implementations of cryptosystems allow an attacker to derive the secret key with very low effort - an algorithm which is strong with respect to conventional cryptanalytic attacks can be useless if it cannot be implemented

securely [9]. Side-channel attacks address ciphers implementations.

**Power analysis attacks** are based on the assumption that the instantaneous power consumption of a circuit is dependent to some small extent on instructions and processed data. Such patterns can be detected also measuring the electromagnetic radiation of the unit. Simple power-analysis attacks exploit instruction dependence where every instruction has its unique power-consumption trace. Such an attack typically targets implementations which use key-dependent branching. For example, one can exploit a strong relationship between Hamming weight of the processed data and the power-consumption trace [9][10]. The leakage of Hamming weight information is used to determine the secret key. Masks are used in implementations that try to achieve protection against differential power-analysis attacks.

**Differential power-analysis** correlates processed data with instantaneous power consumption. Output(s) of the real physical device and output(s) of a hypothetical model (based on a hypothetical key) of the device are correlated. If the hypothetical model only outputs a single value (i.e. it predicts the power consumption of the real device for only one moment in time), then the attack is called *first-order differential power-analysis attack*. If a model can output more values then such an attack is called a *higher-order differential power-analysis attack*. For the two most common types of block ciphers, Feistel and Substitution-Permutation Networks (SPNs), different hypothetical models can be developed and the differences between the two structures will only have an impact on dedicated hardware implementations. However it is easier to perform effective differential power attacks on Feistel ciphers rather than on SPN networks [9].

**Timing analysis**. Information is gained based upon how long encryption takes, and used to reveal the algorithm, key, or data. Particularly useful against the smart card, that measures differences in electrical consumption over a period of time when a microchip performs a function to secure information. This technique combined with differential power analysis can be used to gain information about key computations used in the encryption algorithm and other functions related to security. The technique can be less effective by introducing random noise into the computations, or altering the sequence of the executables to make it harder to monitor the power fluctuations.

**Fault Analysis**. Using this attack, specific faults are introduced into the technology (e. g. smart cards) which can help to reveal the keys. It is also possible to force errors to occur during encryption or decryption, and these errors can lead to hardware faults or software error messages that give away information about the key of the cipher. Different evaluation methodologies have not concentrated to any great extent on side-channel attacks. This is because, although they are very important, there is currently little theoretical strategy one can use to assess such attacks. It is left to the hardware/software designer to implement these encryption algorithms without leaving the system open to such attacks (i.e., by masking data and/or introducing randomness into the order or function of inherent logic operations) [9]. In this context, for instance, in the evaluation of primitives submitted to NESSIE only if a side-channel attack applies, regardless of implementation, is considered as a selection criterion [10].

#### 2.1.4. Systems and their characteristics

A **distributed system** is a system composed of several computers which communicate through computer network(s), hosting processes that use a common

set of distributed protocols to assist the coherent execution of distributed activities [11].

A **real-time** (RT) system is a system [11] for which the progression is specified in terms of *timeliness* requirements dictated by the environment. Three classes of real-time systems are defined: *hard* real-time systems, where timing failures are to be avoided (e.g. on-board flight control systems); *soft* real-time systems, where occasional timing failures are acceptable (e.g. on-line reservation systems) and *mission-critical* real-time systems, where timing failures should be avoided and occasional failures are handled as exceptional events (e.g. air-traffic control system) [11].

The **system-of-systems** concept describes the large-scale integration of many independent, self-contained systems in order to satisfy a global need. Systems-of-systems are characterized by *operational independence* of elements (components operate independently), *managerial independence* of elements (the component systems maintain a continuing operational existence that is independent of the system-of-systems), *evolutionary development* (functions and purposes can be added, removed, and modified), *emergent behaviors* (the system-of-systems performs functions and carries out purposes that do not reside in any component system) and *geographic distribution* (component systems mainly interact through the exchange of information) [12].

#### 2.2. Security as requirement for dependable systems

As defined in the Terminology section, dependability relies on fault prevention, fault tolerance, fault removal and fault forecasting and addresses threats as [5]:

*Development faults* such as software flaws, hardware errata, malicious logic; *Physical faults* generated by product defects, physical deterioration;

*Interaction faults* e.g. physical interference, input mistakes, attacks including viruses, worms, and intrusions.

Interaction faults are all *operational* faults [5] as they occur during the use phase, and they are all *external* as they are caused by the environment. Most of them are *human-made* (e.g. configuration faults, reconfiguration faults), but they can be caused also by external factors such as cosmic rays.

Interaction faults are more common with the development of more complex distributed systems such as *system-of-systems*. An example is the Internet – a collaborative system-of-systems. Internet component sites collaboratively exchange information using documented protocols. This concept can be considered in other fields as well. For instance integrated air defense system consists of geographically distributed network of semi-autonomous elements (e.g. surveillance systems, radars, launch batteries, control systems). All these components are tied together by a communication network with command and control applied at local, regional and national centers [12]. Real-time communication is required in order to consider the system dependable.

Systems-of-systems cannot deliver all their services without *communication*. Because the elements of the system-of-systems are independent, i.e. from energy point of view for instance, they collaborate only through *information exchange*.

For an interaction fault to have an impact on the functionality of the system, usually a prior presence of a *vulnerability* is required. Such vulnerability can be an internal fault that enables an external one to harm the system. Vulnerabilities can be development or operational faults, and they can be malicious or non-malicious.

Based on the above examples we can distinguish two ways to exploit vulnerabilities of a system-of-systems through the information exchange process:

- by faulty information (e.g. a faulty component sends incorrect data deliberate or not deliberate - to other(s) components, or the response time overcomes the defined requirements).

- by *faulty communication* (e.g. due to failures in communication or due to malicious faults when malicious attempts to manipulate the communications are successful).

For the second way, when vulnerabilities are exploited due to *faulty communication*, security is required to address malicious attempts using cryptographic algorithms for assuring confidentiality, data integrity, entity and data authentication, etc.

This is the *first* motivation supporting the need for security in dependable systems. Security is needed to avoid failure of systems due to errors that could be caused in *the system* by interaction faults (e.g. malicious faults in system implementation).

We are going to bring a *second* motivation for the need for security in dependable systems. This comes in the context of fault tolerance mechanisms developed in dependable systems. Fault tolerance mechanisms in such systems also require protection i.e. security.

Fault tolerance aims to avoid failures using error detection and system recovery. Fault tolerance techniques are designed to improve the availability of the distributed systems, based on adaptation to changing run-time conditions. Given the transition from a single application per machine to distributed systems, new problems have to be solved (e.g. new type of faults left after fault removal). These problems are generated by the interaction between different components of a system, components that usually have a different location, and rely on communication channels for the normal operation of the applications [13]. New types of fault tolerance techniques have to address new interaction problems and they need to adapt to the changes in the environment (e.g. due to crash fault, or due to dynamic nature of the system). Proactive techniques (such as software rejuvenation) rely on monitoring the behavior and the resources of the system, in order to predict possible failures and to trigger preventive actions accordingly. Some of the decisions generated by the fault tolerance mechanisms are based on monitoring [14], detection, or prediction of the behavior of the components of the distributed system [15]. However, if a third party can modify the input data for monitoring, detection or prediction of fault tolerance mechanisms the decisions taken based on those data are compromised (this is an example of exploited vulnerability using faulty information) [16]. In the same time, by faulty communication, if messages are manipulated (modified or duplicated by an unauthorized third party) the fault tolerance mechanism can trigger an unsuitable action, or the component executing recovery action may execute a wrong action [17]. Furthermore the overall purpose of fault tolerance (improving reliability, dependability) can be compromised.

We can conclude that a dependable system needs security both for the part delivering services for its normal functionality and for the fault tolerance mechanisms designed to assure the dependability of the system.

Authorization, authentication, data integrity, confidentiality required for security purposes are achieved by implementing cryptographic tools. In Chapter 3 cryptographic tools are addressed.

# 2.3. Intrusion tolerance approaches. Using fault tolerance to address security issues

Introduced with malicious objectives, **malicious faults** intend to alter the functionality of the system during use. The goals of malicious faults [5] are:

- to disrupt or halt service, causing denials of service;

- to access confidential information;

- or to improperly modify the system.

Malicious faults are grouped in two classes: **malicious logic faults** and **intrusion attempts**. First class covers (internal) development faults e.g. Trojan horses, and operational faults e.g. viruses.

*Intrusion attempts* are operational (external) faults, so interaction faults. Intrusion attempts may use physical means such as radiations, variation on temperature, power fluctuation to cause faults.

Even if the fault tolerance techniques and mechanisms do not always consider malicious faults (generated by intrusion attempts on the security of the system by both insiders and outsiders), fault tolerance techniques are used to build intrusion-tolerant systems.

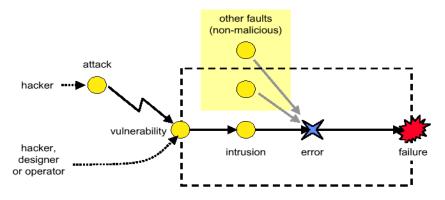

To address the specificity of malicious faults, the fault-error-failure model (represented in figure 2.1.) has been extended to security. The extended model (figure 2.5) presents the manifestation mechanism of a successful attack exploiting existing vulnerabilities, which results in intrusion.

**Intrusions** are resulting from (at least) partially successful **attacks** exploiting existing **vulnerabilities**.

Figure 2.5. Attack-vulnerability-intrusion chain [18]

Besides extending the fault model, based on the dependability means (fault prevention, fault tolerance, fault removal and fault forecasting) presented in the dependability tree in figure 2.3, security means were defined in *MAFTIA (Malicious and Accidental Fault Tolerance for Internet Applications)* project [19]. Figure 2.6 summarizes security means and the methods to handle attacks, vulnerabilities and intrusions.

The use of fault tolerance techniques to built intrusion-tolerant systems has been explored in the European funded research project MAFTIA. Intrusion detection concerns the set of practices and mechanisms used towards detecting errors that may lead to security failure, and/or diagnosing attacks.

**Intrusion tolerance** is the ability of a system to continue providing a secure service (even degraded) despite the presence of malicious faults (i.e.

27

deliberate attacks on the security of the system by both insiders and outsiders) [19]. In MAFTIA, intrusion tolerance is achieved using an intrusion-tolerant group communication protocol and an intrusion-tolerant distributed authorization service. MAFTIA uses fault masking to achieve intrusion tolerance and does not address fault removal or system reconfiguration.

|             |                                                                                                   | Attack                                                                         | Vulnerability                                                                                   | Intrusion                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Prevention  | How to prevent<br>the occurrence<br>or introduction<br>of                                         | Deterrence, laws,<br>social pressure,<br>secret service                        | Semi-formal and<br>formal<br>specifications,<br>rigorous design<br>and<br>management#           | Firewalls,<br>authentication,<br>authorization<br>(+attack prevention<br>and vulnerability<br>prevention) |

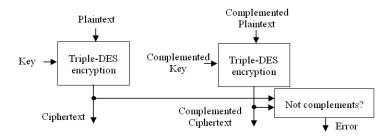

| Tolerance   | How to provide<br>a service<br>capable of or<br>implementing<br>the system<br>function<br>despite | Vulnerability<br>prevention<br>Vulnerability<br>removal<br>Intrusion tolerance | = intrusion<br>tolerance                                                                        | Detection/recovery/<br>masking, + intrusion<br>tolerance for fault<br>management* #                       |