# Information Processing using Liquid State Machines based on Spiking Neurons

Teză destinată obținerii titlului științific de doctor inginer la Universitatea "Politehnica" din Timișoara în domeniul Inginerie Electronica si Telecomunicatii de către

# ing. Radu Mirsu

Conducător științific: Referenți științifici: prof.univ.dr.ing. Virgil Tiponut prof.univ.dr.ing. Dorian Cojocaru prof.univ.dr.ing. Gavril Toderean prof.univ.dr.ing. Ivan Bogdanov

Ziua susținerii tezei: 26.11.2011

Seriile Teze de doctorat ale UPT sunt:

- 1. Automatică

- 2. Chimie

- 7. Inginerie Electronică și Telecomunicații 8. Inginerie Industrială

- tă 9. Ingir

- 3. Energetică

4. Ingineria Chimică

- 9. Inginerie Mecanică

- 10. Ştiinţa Calculatoarelor

- 5. Inginerie Civilă 11. Știința și Ir

- 6. Inginerie Electrică

- 11. Știința și Ingineria Materialelor

Universitatea "Politehnica" din Timişoara a iniţiat seriile de mai sus în scopul diseminării expertizei, cunoştinţelor şi rezultatelor cercetărilor întreprinse în cadrul şcolii doctorale a universității. Seriile conţin, potrivit H.B.Ex.S Nr. 14 / 14.07.2006, tezele de doctorat susținute în universitate începând cu 1 octombrie 2006.

#### Copyright © Editura Politehnica – Timişoara, 2011

Această publicație este supusă prevederilor legii dreptului de autor. Multiplicarea acestei publicații, în mod integral sau în parte, traducerea, tipărirea, reutilizarea ilustrațiilor, expunerea, radiodifuzarea, reproducerea pe microfilme sau în orice altă formă este permisă numai cu respectarea prevederilor Legii române a dreptului de autor în vigoare și permisiunea pentru utilizare obținută în scris din partea Universității "Politehnica" din Timișoara. Toate încălcările acestor drepturi vor fi penalizate potrivit Legii române a drepturilor de autor.

România, 300159 Timişoara, Bd. Republicii 9, tel. 0256 403823, fax. 0256 403221 e-mail: editura@edipol.upt.ro

# Acknowledgements

This doctoral thesis was supported in part by POSDRU/6/1.5/S/13 strategic grant, ID6998, financed from European Social Fund "Investing in people" in the Human Resources Development Operational Programme 2007-2013.

This work was partially supported by the following grants:

"Noi metode de analiză și recunoaștere a expresiei faciale", Program PNII, IDEI, Proiecte de cercetare exploratorie, cod 945/2008, finantat de Unitatea Executivă pentru Finanțarea Învățământului Superior și a Cercetării Stiințifice Universitare (UEFISCSU), Nr. Contract: 599/19.01.2009.

"Research on Emotional Facial Expression recognition in Complicated Environment", Program PNII, CAPACITATI, Modul III, proiecte de cercetare bilaterale, România-China, 39-5/2008, finantat de Autoritatea Națională pentru Cercetare Științifică (ANCS), Nr. Contract: 222/15.04.2009

I would like to thank my advisor, Prof. Dr. Eng. Virgil Tiponut, for the countless advices and work hours that he has put into this research. He has been a great colleague and friend showing optimism and high morale when needed most. I also would like to thank Prof. Dr. Eng. Catalin Caleanu with whom I have collaborated at GPU programming and Gabor filtering tasks.

I also owe my gratitude to the Applied Electronics Department Director, Prof. Dr. Eng Ivan Bogdanov, to Electronics and Telecommunications Faculty Dean, Prof. Dr. Eng. Marius Otesteanu, and to my fellow colleagues, PhD Candidates: Sebastian, George, Zoltan, Robert, Daniel and Mihai.

Special thanks to the PhD committee, Prof. Dr. Eng Dorian Cojocaru University of Craiova, Prof. Dr. Eng. Gavril Toderean, Technical University of Cluj-Napoca and Prof. Dr. Eng Ivan Bogdanov, Politehnica University of Timisoara for their evaluations and suggestions regarding the thesis.

I would like to thank my loving wife Betina, my parents and my sister Adina for their never ending understanding, patience and support.

Timişoara, November 2011

Radu Mirsu

This doctoral thesis was supported in part by POSDRU/6/1.5/S/13 strategic grant, ID6998, financed from European Social Fund "Investing in people" in the Human Resources Development Operational Programme 2007-2013.

#### Mirsu, Radu

# Information Processing using Liquid State Machine based on Spiking Neurons

Teze de doctorat ale UPT, Seria 7, Nr. 41, Editura Politehnica, 2011, 120 pagini, 64 figuri, 7 tabele.

ISSN: 1842-7014

ISBN: 978-606-554-376-8

Cuvinte cheie: spiking neural networks, Liquid State Machines, liquid computing, Gabor filtering, dynamic neurons, neural modelling, neurons on GPU, parallel processing

#### Rezumat,

Spiking neural networks are introduced as the third generation of neural models. They are dynamic models that potentially have much more processing power than classic neural networks. This thesis presents a novel approach to perform Gabor filtering using Liquid State Machines based on Spiking Neurons. The Liquid State Machine is a powerful architecture that is capable of performing universal computations without being trained on specific data. It is the job of special readout units to interpret the computation results and map them on specific target functions. In addition, the thesis presents tools that allow fast simulating of large neural networks by running the simulation in parallel on a GPU.

## CONTENTS

| Acknoledgements<br>Abstract<br>Contents<br>List of Figures                                                | 4<br>5   |

|-----------------------------------------------------------------------------------------------------------|----------|

| <b>1. Introduction</b> 1.1. Research Motivation         1.2. State of the art         1.3. Thesis Outline | 11<br>13 |

| 2. Spiking Neural Networks                                                                                | 10       |

| 2.1 Synapses                                                                                              |          |

| 2.2 Dynamic Synapses                                                                                      |          |

| 2.2.1. Depressing Synapse                                                                                 |          |

| 2.2.2. Synapse Delay                                                                                      |          |

| 2.2.3. Facilitating Synapse                                                                               |          |

| 2.2.4. Recursive Model for Dynamic Synapse                                                                |          |

| 2.3. Spiking Neuron Models                                                                                |          |

| 2.3.1. The Biological Neuron                                                                              |          |

| 2.3.1.1. Spike Generation                                                                                 |          |

| 2.3.1.2. Refractory Period<br>2.3.2. Integrate and Fire Neuron                                            |          |

| 2.3.3. Integrate and Fire with Burst Neuron                                                               |          |

| 2.3.4. Integrate and Fire with Adaptation Neuron                                                          |          |

| 2.3.5. Resonate and Fire Neuron                                                                           |          |

| 2.4. Coding with Spikes                                                                                   |          |

| 2.4.1. Spiking Neuron as Context Detector                                                                 | 36       |

| 2.4.2. Content Addressable Memory with Spiking Neural Networks                                            | 38       |

| 2.4.2.1. Choosing Spike Contexts                                                                          | 38       |

|                                                                                                           |          |

| 3. Modelling and Simulation                                                                               |          |

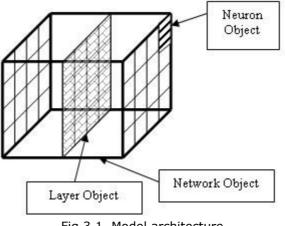

| 3.1. Model Objects                                                                                        |          |

| 3.1.1. Network Object                                                                                     |          |

| 3.1.2. Layer Object                                                                                       |          |

| 3.2. Model Functions                                                                                      |          |

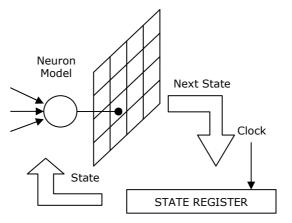

| 3.2.1. Simulation Functions                                                                               |          |

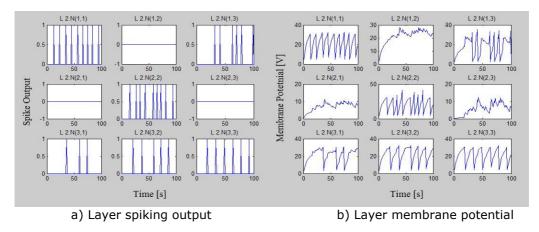

| 3.2.2. Vizualisation Functions                                                                            |          |

| 3.2.2.1. Vizualising Neural Time Traces                                                                   |          |

| 3.2.2.2. Vizualising Neural Spike Rates                                                                   |          |

| 3.2.2.3. Vizualising Neural Synchrony                                                                     |          |

| 3.3. Parallelizing the Model                                                                              | 47       |

| 3.3.1. Choosing the Number of Slaves<br>3.3.2. Results         |      |

|----------------------------------------------------------------|------|

| 4. GPU Accelerated Model for Spiking Neural Networks           | 53   |

| 4.1. General Purpose GPU Computing                             |      |

| 4.1.1. Early GPU Computing.                                    |      |

| 4.1.2. NVIDIAs CUDA Architecture                               |      |

| 4.1.3. Simple CUDA Example                                     | 55   |

| 4.2. Spiking Neural Network CUDA Model                         |      |

| 4.2.1. Model Architecture                                      |      |

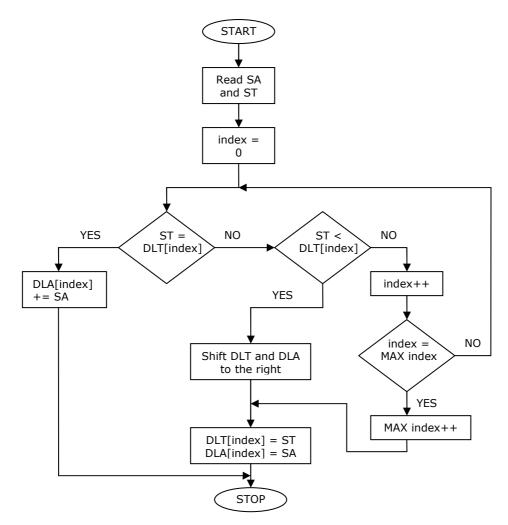

| 4.2.2 Delay Line Implementation                                | 58   |

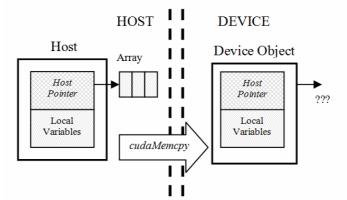

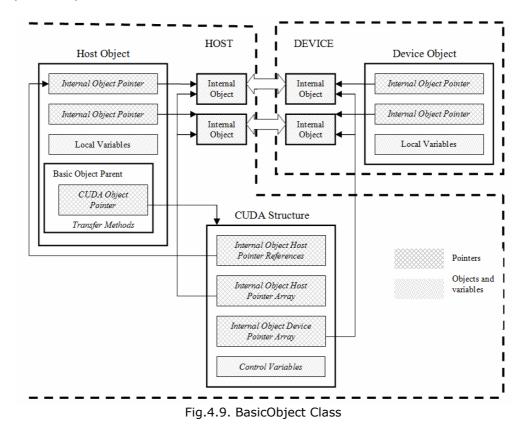

| 4.2.3. Moving Objects between Host Computer and Device GPU     | 61   |

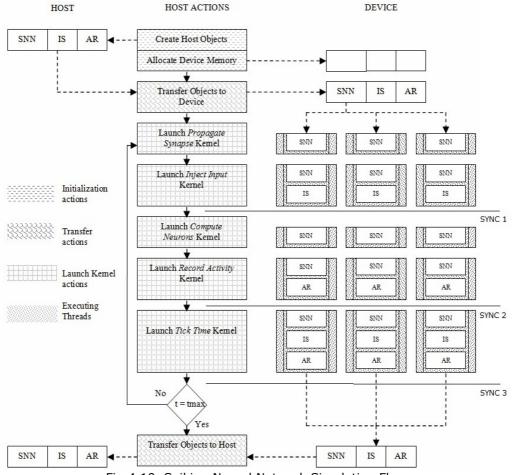

| 4.2.4. Simulating the Model                                    | 63   |

| 4.2.5. Simulation Results                                      | 65   |

| 4.3. Improved CUDA Model                                       | 66   |

| 4.3.1. Minimizing the number of branches                       | 66   |

| 4.3.2. Merging Kernels                                         |      |

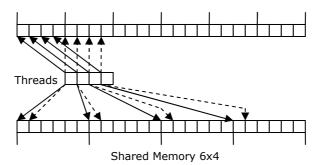

| 4.3.3. Using Shared Memory                                     |      |

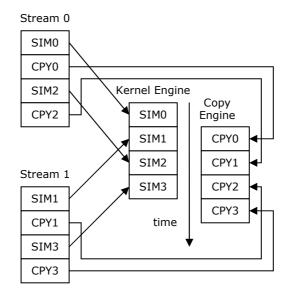

| 4.3.4. Overlapping Computation and Data Transfer               |      |

| 4.3.5. Using Constant Memory and Texture Memory                |      |

| 4.3.6. Simulation Results                                      | 74   |

|                                                                |      |

| 5. Liquid State Machine And Liquid Computing                   | 75   |

| 5.1. Introduction                                              | 75   |

| 5.2. Liquid State Machine Architecture                         | 75   |

| 5.2.1. Recurrent Liquid Medium                                 | 76   |

| 5.2.2. The Read-Out Units                                      | 77   |

| 5.3. Liquid States. Separation Property                        | 78   |

| 5.4. The Parallel Perceptron Readout Unit.                     |      |

| The p-Delta Learning Algorithm                                 |      |

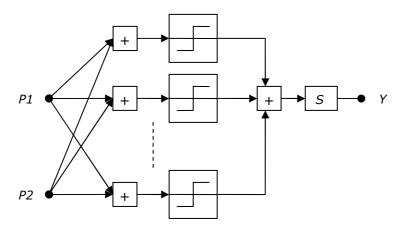

| 5.4.1. The Parallel Perceptron                                 |      |

| 5.4.2. The Single Perceptron Delta Rule                        | 80   |

| 5.4.3. The Parallel Perceptron p-Delta Rule                    |      |

| 5.4.4. Adaptive Learning Rate                                  |      |

| 5.4.5. Greedy vs. Not Greedy                                   | 82   |

| 5.4.6. Adaptive Noise Margin Control                           |      |

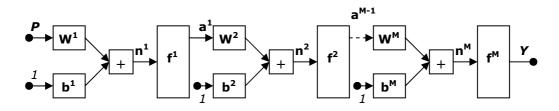

| 5.5. The Feedforward Readout Unit. Backpropagation             | 88   |

|                                                                |      |

| 6. Gabor Filtering using Liquid State Machines                 |      |

| and Spiking Neurons                                            |      |

| 6.1. Introduction                                              |      |

| 6.2. Gabor Filtering                                           |      |

| 6.3. Filtering with Liquid State Machines                      |      |

| 6.3.1. Input Signals                                           |      |

| 6.3.2. Spike Generator with Shifting Phase                     |      |

| 6.3.3. Estimating Gabor Coefficients with Liquid State Machine |      |

| 6.3.3.1. Approximation Accuracy                                |      |

| 6.3.3.2 Approximation Speed                                    |      |

| 6.3.3.3. LSM Performance                                       | .103 |

| 7. Conclusions and Contributions                                   |     |

|--------------------------------------------------------------------|-----|

| 7.1.1. Spiking Neural Networks                                     |     |

| 7.1.2. MATALB simulation framework                                 | 105 |

| 7.1.3. Parallel MATLAB framework and GPU accelerated framework     | 105 |

| 7.1.4. Liquid State Machines and p-Delta Learning Rule             | 106 |

| 7.1.5 Extracting Gabor Coefficients from images using Liquid State |     |

| Machines based on Spiking Neurons                                  |     |

| 7.2. Future Work                                                   | 107 |

| 7.3. Theoretical Contributions                                     |     |

| 7.4. Practical Contributions                                       | 109 |

| 7.5. Publications List                                             | 110 |

| Refferences                                                        | 112 |

## LIST OF FIGURES

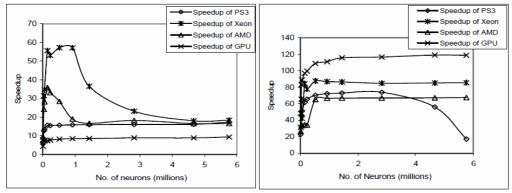

- Fig. 1.1. Parallel Implementations for simulating Spiking Neural Networks

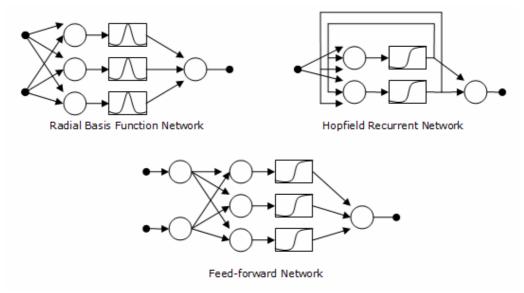

- Fig. 2.1. Second Generation Neural Networks

- Fig. 2.2. Biological Neural Network

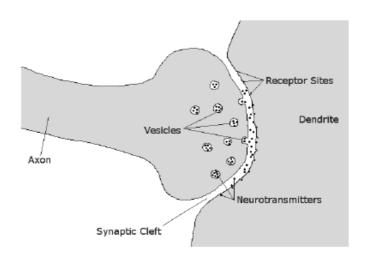

- Fig. 2.3. Biological Synapse

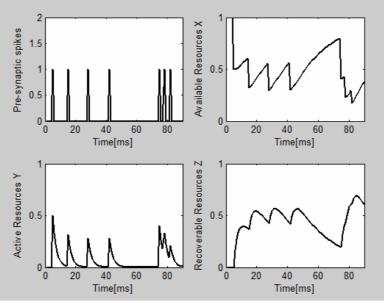

- Fig. 2.4. Synapse Dynamic functionality

- Fig. 2.5. Hodgkin-Huxley Neuron Model

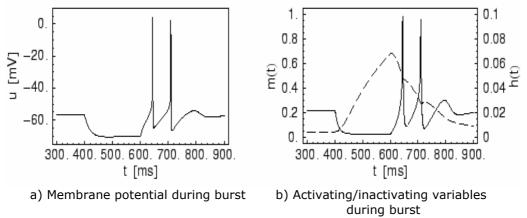

- Fig. 2.6. Activation and inactivation variables

- Fig. 2.7. Functioning of the Neuron. Generating spikes

- Fig. 2.8. Integrate and fire neuron model

- Fig. 2.9. Calcium Current Effect

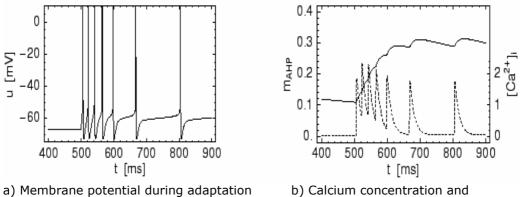

- Fig. 2.10. Adaptation Mechanism

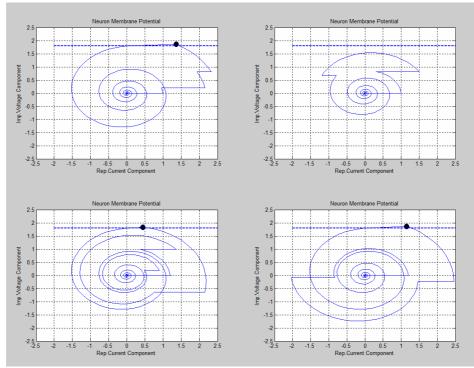

- Fig. 2.11. R&F Neuron Membrane Potential

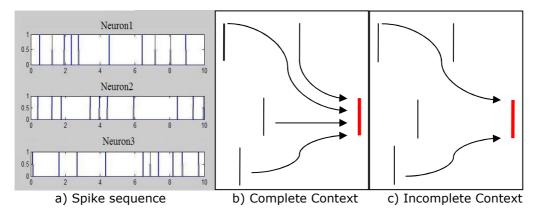

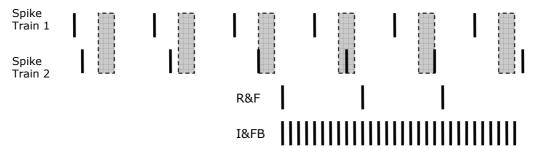

- Fig. 2.12. Spatial-temporal spike sequences. Complete and incomplete spike contexts

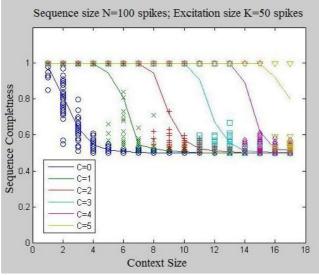

- Fig. 2.13. Context size influence on performance.

- Fig. 3.1. Model architecture

- Fig. 3.2. Network and Layer Objects

- Fig. 3.3. Updating the network state

- Fig. 3.4. Neuron Object

- Fig. 3.5. Network spiking activity object

- Fig. 3.6. Visualization of spiking and potential traces

- Fig. 3.7. Visualization of the average spike rate as image

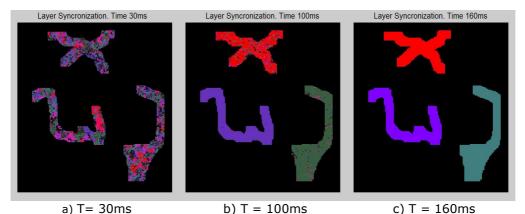

- Fig. 3.8. Visualizing Neural Synchrony

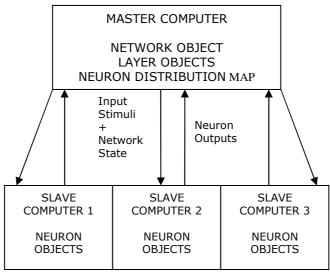

- Fig. 3.9. Distributed Model on a network of Computers

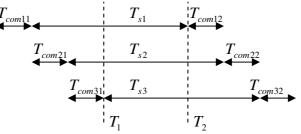

- Fig. 3.10. Master-Slave Interaction

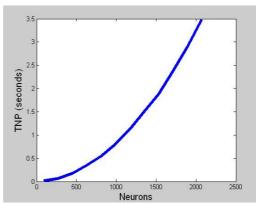

- Fig. 3.11. Non-Linear simulation time as a function of the number of neurons

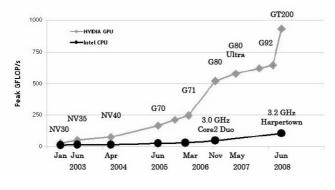

- Fig. 4.1. CPU vs. GPU evolution

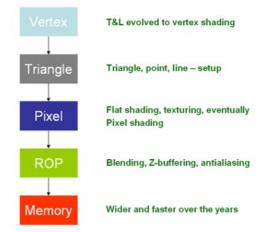

- Fig. 4.2. OpenGL graphics processing pipeline.

- Fig. 4.3. Simple CUDA parallel program

- Fig. 4.4. Kernel Launch

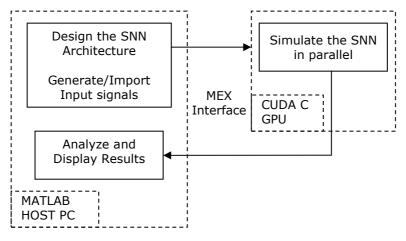

- Fig. 4.5. MATLAB-CUDA C interfacing

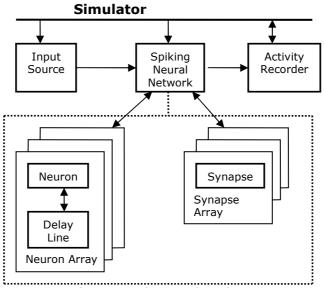

- Fig. 4.6. Spiking Neural Network Architecture

- Fig. 4.7. Delay Line Functionality

- Fig. 4.8. Incomplete Object transfer

- Fig. 4.9. BasicObject Class

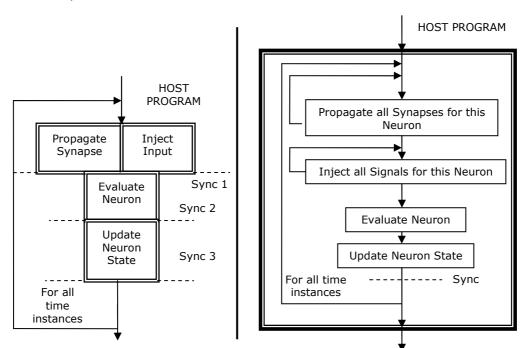

- Fig. 4.10. Spiking Neural Network Simulation Flow

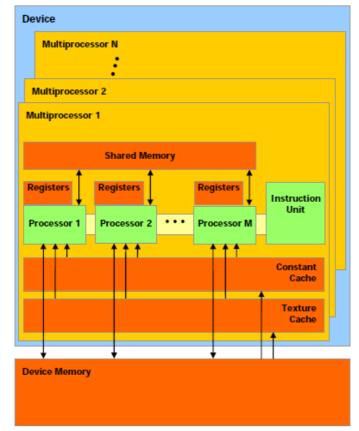

- Fig. 4.11. GPU architecture

- Fig. 4.12. Merging Kernels

- Fig. 4.13. Two versions for implementing the delay line inside shared memory

- Fig. 4.14. Overlapping computation and data transfer

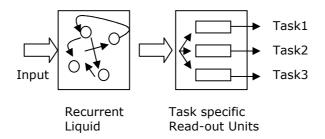

- Fig. 5.1. Liquid State Machine architecture

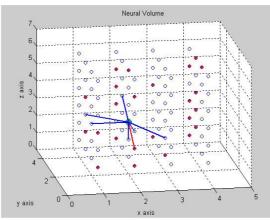

- Fig. 5.2. Liquid State Machine implemented by a recurrent Spiking Neural Network

- Fig. 5.3 Parallel Perceptron Readout Unit

- Fig. 5.4. Multi-Layer Feedforward Readout Unit

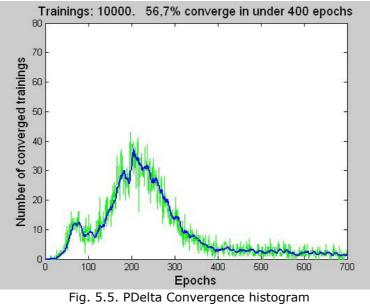

- Fig. 5.5. PDelta Convergence histogram

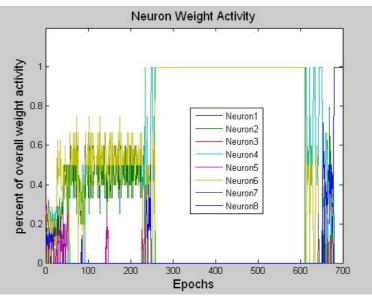

- Fig. 5.6. Distribution of weight activity ("greedy" approach)

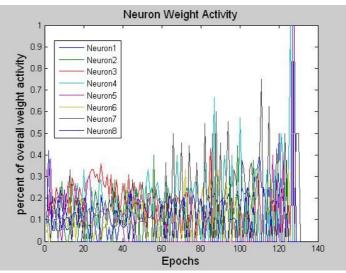

- Fig. 5.7. Distribution of weight activity ("not greedy" approach)

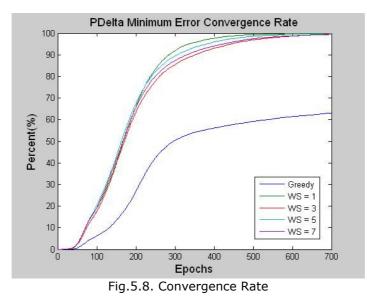

- Fig. 5.8. Convergence Rate

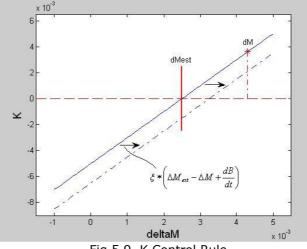

- Fig. 5.9. K Control Rule

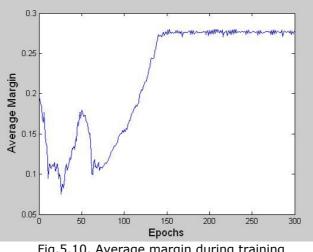

- Fig. 5.10. Average margin during training

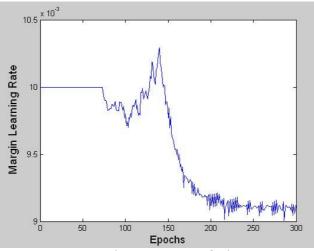

- Fig. 5.11. Margin learning rate mlr during training

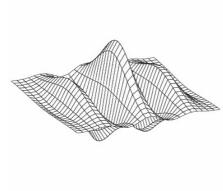

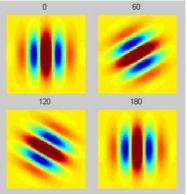

- Fig. 6.1. 2D Gabor Filter Kernel

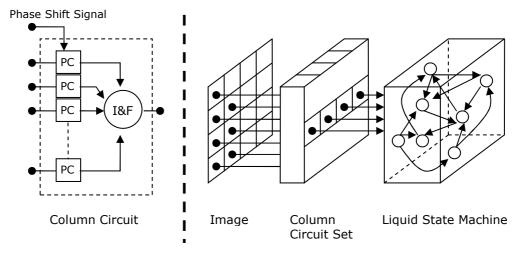

- Fig. 6.2. Time-Multiplexing the Input Signals

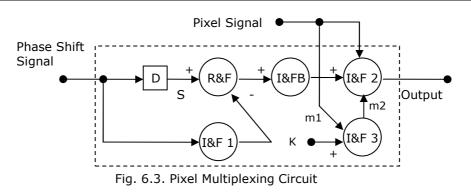

- Fig. 6.3. Pixel Multiplexing Circuit

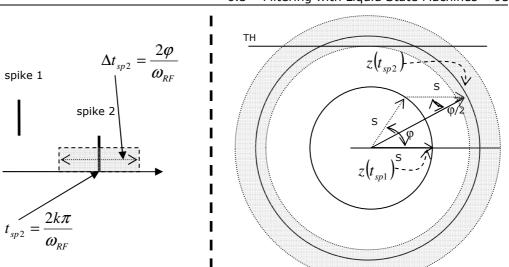

- Fig. 6.4. Membrane Potential of R&F Neuron

- Fig. 6.5. Activation of R&F Neurons

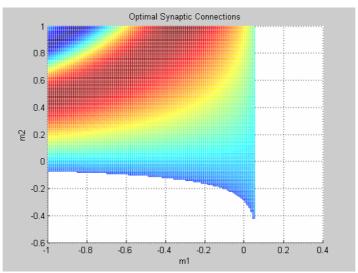

- Fig. 6.6. Optimization of m1 and m2 synaptic connections

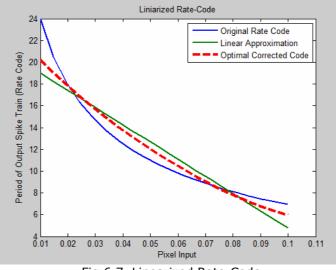

- Fig. 6.7. Linearized Rate-Code

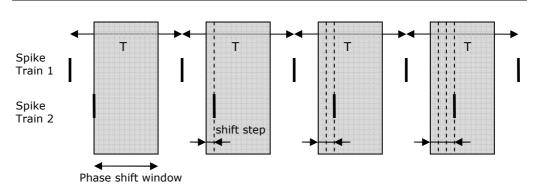

- Fig. 6.8. Shifting Phase Spike Trains

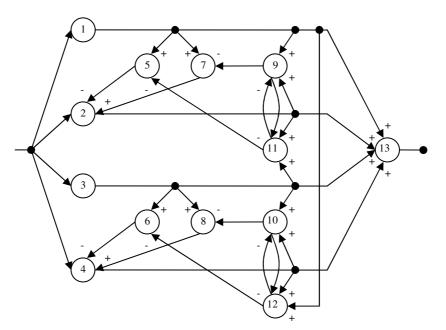

- Fig. 6.9. Shifting Phase Circuit 1

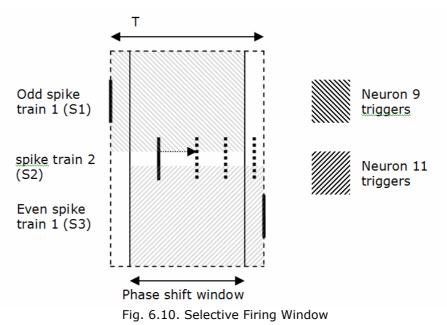

- Fig. 6.10. Selective Firing Window

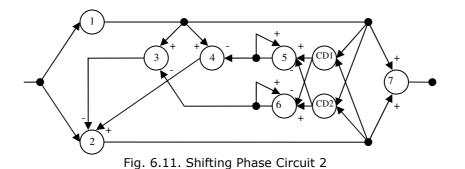

- Fig. 6.11. Shifting Phase Circuit 2

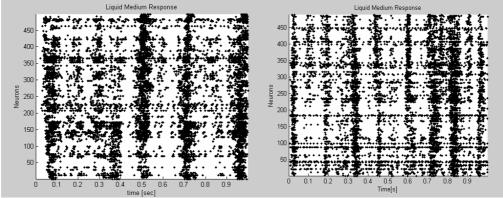

- Fig. 6.12. Spiking Activity of Liquid Medium

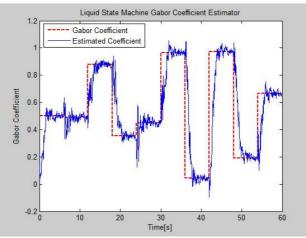

- Fig. 6.13. Estimating Gabor Coefficients

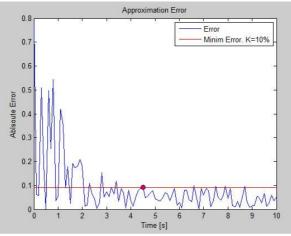

- Fig. 6.14. Computing the Approximation Error

# **1. INTRODUCTION**

## **1.1. Research Motivation**

Networks based on spiking neurons are thought to be the third generation of neural networks. This classification is done by Maass in [1] as follows:

- Generation 1. Binary networks built from perceptrons that are able to perform simple classifications and compute digital functions

- Generation 2. Networks with real-numbered outputs that could be used as universal approximators to any degree of precision.

- Generation 3. Spiking neural networks (SNN).

In contrast with previous generations, spiking neural networks return to models that resemble the biological neuron, and capture its dynamic spiking functionality. Even though the mathematical model for a biological neuron is an old discovery [2], it was left aside for decades because its complexity led to computationally overwhelming problems. Recently, with the continuously growing processing power of computers, researchers are returning to spiking models in order to find solutions to problems that were not solved by previous generations of neural networks. Some of the disadvantages of the classical models are presented in the following paragraphs. These combined with the numerous advantages of the new spiking models represented a strong motivation for embracing this research track.

In case of older models it was assumed that the intricate details of the neuron behavior are irrelevant to information processing. If biological neurons used simple techniques to encode information, like rate coding, modeling by using an activation function would be sufficient. However, recent research shows that it is very likely that the dynamic behavior of the spiking neurons (tonic or phasic spiking, bursting, spike frequency adaptation, spike latency, sub-threshold oscillations, resonance, integration and coincidence, rebound spikes or bursts, bistability or threshold variations) plays an important part in information processing [81], [83]. These behaviors are well presented in [3]. Also, none of these behaviors were achievable by the older generations of neural networks.

Several mechanisms are present at synapse level. Observations made in [4] show that a synapse can adjust its strength depending on the timing between the presynaptic spike and the postsynaptic spike. This way, two neurons that are both firing within a short time interval can lock and fire in synchrony, thus creating a natural implementation of Hebbian learning. This property requires that the neuron model is spiking.

Research in the field of neuropsychology is continuously unveiling information regarding the technique used by the brain to code and process information. These discoveries, most often, are incompatible with the older neural models and cannot be applied directly because there is not a direct relationship between the biological observations and the elements of the model. In the case of spiking neural networks this discrepancy is eliminated.

#### 12 Introduction - 1

Spiking neural networks have another property that the traditional models do not. Since the spiking models are dynamic time-based models they can oscillate and can exhibit resonant behavior. In [5], [6] a spiking neural network achieves signal multiplexing by using resonate and fire neurons that are able to lock and synchronize with specific spike frequencies. In [7], Izhihevich introduces another interesting property of spiking neurons called "polychrony" different from "synchrony". If synchrony refers to a group if neurons firing at the same time (or within a small time window), polychrony refers to a group of neurons that fire in the same order and with the same relative timing. This property is also referred to as temporal grouping in papers like [8], [9], [10], [11], [12], and seems to play a crucial part in how the central nervous system performs computations. Polychrony is possible due to the synapse propagation delays which cause the spiking network to generate spatial-temporal spike sequences when stimulated. The complex dynamics of an intricately connected network could lead to a potentially unlimited set of spike sequences. Therefore, a spiking neural network could implement a memory that has a storing capacity significantly bigger than its number of synapses.

Oscillation and synchrony are properties that are considered to play an important part in image segmentation and object binding [13], [14]. Csibra and Davis [13] observe a close relationship between object binding and 40Hz (gamma band) oscillations evident in the brain of an 8 months infant. This is the same age when the behavior of the child start to exhibit perception of spatially separated visual features. Oscillations can also play an important role in short term memory according to Jensen in [15] and [16]. Here it is demonstrated that oscillations in the alpha band (9 to 12Hz) have an increasing peak that related to the number of items retained by the short term memory.

Spiking neural networks are obviously an improvement compared to the more traditional models. Backing up this statement is the fact that spiking networks are able to perform all tasks and exhibit all behaviors present at the first generation and the second generation of networks. In addition, the above paragraph describes new behaviors that are new and are very promising from the information processing perspective. Also, these models are much more similar to the biological neurons. This fact is encouraging because nature has repeatedly proven to be the ultimate designer. Because all good things come with a price, spiking neural models have their own disadvantages:

- The complexities of the individual neuron and also the large size of the networks that need to be simulated require huge amounts of computational resources. This is even more critical when several simulations need to be performed during an optimization. The limited speed of the simulator was also the first big challenge of this thesis. A satisfactory solution to this problem was to use a GPU to accelerate the simulation in hardware. Of course, regardless of the simulation platform, there will always be a compromise between the sizes of the network, the complexity of the individual neuron, the duration of the simulation and the step size of the solver.

- Spiking neural networks are systems with extremely complex dynamic behavior. The major difficulty in understanding how this behavior can process information. Investigating the functionality of the network by using rigorous mathematical tools that could directly pinpoint the solution to the problem is improbable. More likely to be successful are evolutionary techniques that allow the system to evolve on its own.

- Because these models are relatively new there is a shortage of knowledge, algorithms or tools that serve the utilization of such networks.

- The spiking neural networks are very successful in the real world. However, it should be always kept in mind that the brain has around 30 billion neurons and each neuron is served by several thousands of synapses. These figures that are beyond any present simulation capabilities. It is unclear if similar performances can be obtained using a reduced size spiking neural network even for significantly simpler applications.

## **1.2. State of the Art**

There is a continuous struggle to find new architectures and solutions to designing a biologically inspired neural network that is computationally powerful. It is the research area where several adjacent study fields collide (i.e. computer science, neuroscience, biophysics, and machine learning). In [17] Jaeger and Maass present that there are currently two approaches when trying to design a biologically inspired neural network. The first method, the bottom-up way, investigates the structure and the dynamic functionality of the brain by observation. Then it uses mathematical tools to try and capture dynamical patterns and special behaviors that are believed to be significant to information processing. The method is called bottom-up because it deduces the method and flow of the computation by examining the functioning of the hardware. Alternately, we can use the top-down method. In this case we start from known computing techniques and design submodules of biologically inspired networks, each suitable for solving a part of the computational task. In contrast to the bottom-up method, the top-down approach fits the hardware to the method. Obviously, the top-down method has a higher chance of deviating from the actual biological architecture.

This thesis focuses on a new type of architecture called Liquid State Machine (LSM) introduced by Maass, Natschlaeger and Markram in [18]. It is a new design that adopts the principle of reservoir computing. In parallel, but independently, a similar architecture called Echo State Networks (ESN) was developed by Jaeger [19], [86]. The two models are similar in principle but were designed with different applications in mind. Liquid State Machines tend to be general and are formulated within the mathematical frameworks of dynamical systems theory and filtering theory. Because the model aims towards a biologically plausible implementation it is restricted to having spiking neurons as computational units that preserve the characteristics of the biological neuron and operate well under noisy conditions. On the other hand, the echo state networks are a particular case of LSM and so the theory applies. However, ESNs are designed to have a higher performance on particular engineering applications that use noiseless artificial neural networks as computing units.

There are several directions of research regarding LSMs and ESNs. The following paragraphs try to determine the most important research tracks and present some state of the art methods and results.

For example, Yamazaki and Tanaka [20] try to find a direct correspondence between the cerebellum and a liquid state machine. In fact they find evidence that the granular layer behaves as a liquid medium (reservoir), while the Purkinje cells which receive signals from the granular layer act as readout units. In [21], different forms of network plasticity are analyzed in an attempt to determine how they affect the dynamic behavior of recurrent spiking neural networks. The paper studies spike timing dependent plasticity (STDP) which is responsible for adapting synaptic strength, and intrinsic plasticity (IP) which is responsible for adapting the excitability of individual neurons. The interaction between the two forms of plasticity maintains the homeostasis of neural activity and stabilizes the LSM.

Joshi [22] demonstrates that a liquid state machine can also be used as a multi-tasking computing machine, where the computations related to all tasks are being performed in parallel by the same liquid medium. It is the duty of several readout units to map the liquid neural activity to the task specific output functions. It is very important to notice that unlike other parallel machines that dedicate separate resources to different tasks, the liquid state machine performs a unified computation of multiple tasks where the same neurons can participate at different tasks at the same time. In [22] it is also shown that the readout units can send feedback of their activity in order to tune up the activity of the liquid medium. The paper also presents an application with good results where a liquid state machine is used at driving electrical motors. In [23], Legenstein and Maass try to determine which properties of the recurrent circuits of spiking neurons are relevant for their computational performance. They also find to methods of analyzing the computational capabilities of spiking neural networks.

Echo state networks are also well used in speech recognition applications as demonstrated by Skowronski and Harris [24]. Here a speech classifier that can recognize words from a small vocabulary is designed by combining an ESN and a state machine. The new classifier outperforms the Hidden Markow Models in regimes of low signal to noise ratios. Article [25] also presents an application with speech recognition that uses spiking neurons arranged in an architecture called "mussilicium". The system contained approximately one thousand spiking neurons and was able to recognize ten spoken words regardless of the speaking speed. The mussilicium however, is not biologically inspired. Instead, it uses spiking neurons in an architecture that is built on more deterministic rules inspired from signal processing and computer science.

In [26], Verstraeten and Schrauwen use a liquid state machine that is trained to perform isolated word recognition. Several techniques for encoding the input signals are tested. The encoding represents a bridge between the actual recorded signals and the liquid state machine. Surprising and also encouraging is the fact that the liquid state machine performs best when the model of the inner ear is used at encoding the vocal signals. This result increases the confidence that the liquid state machine is indeed biologically plausible. Another speech/audio application if presented in [33].

Another field where liquid state machines and echo state networks are applied is grammar and language learning. Tong presents in [27] an application that uses an echo state network to learn grammatical structure. The results are comparable to those obtained by the existing Elman networks. The advantage over the Elman networks is simpler design rules and simpler training algorithms. The Elman networks, which are also recurrent, were able learn internal data representations that were sensitive to linguistic processes by adjusting the synapses of the recurrent connections during a training algorithm. ESNs, like liquid state machines, have a fixed recurrent medium that does not need to be trained. Training occurs only at readout level and is much simpler.

Currently liquid state machines and echo state networks have proven immense potential in several research fields targeting a wide range of applications. As expected some of these applications were more successful at using liquid state machines than others. Consequently, another research track arose that tries to determine what parameters of the liquid medium (reservoir) are most significant for

1.2 - State of the art 15

performance and if these parameters are specific to particular applications. Haykin and Xue [28] present a modified version of echo state network that uses lateral inhibition to improve the richness of the liquid medium dynamics. In [29], the authors present a method for quantifying the richness of the liquid medium dynamics by evaluating the entropy of the echo states. In [30], Dedual and Ozturk present a modified version of the readout units called MACE that is able achieve higher specificity in pattern recognition applications.

The last part of this paragraph is dedicated to implementation and simulation techniques. Currently, there's no single simulation framework that can be considered standard for simulating spiking neural networks. Because the model is computationally demanding one of the biggest issues when choosing or designing a simulation framework is to accelerate it as much as possible. As it will be seen in the following chapters the model is very parallel and so the major trend in SNN simulation is to use a framework that runs on multi-core or GPU parallel architectures. Chapters 3 and 4 present two approaches to parallelize the model, one using a distributed architecture and another using a GPU. In [31] Bhuiyan, Pallipuram and Smith, compare the speed-ups obtained by four parallel architectures: IBM PS3, AMD Opteron, Intel Xeon and NVIDIA GPU [41]. The results of their study are presented in figure 1.1. The speedups obtained with the GPU architecture are very similar to those presented in chapter 4. The numbers, however, cannot be compared directly because the speedup was measured by benchmarking different processors.

Fig. 1.1. Parallel Implementations for simulating Spiking Neural Networks

The left graph in figure 1.1 corresponds to simulations where each individual neuron uses the Izhikevich model, while the right graph contains results of simulations that use the Huxley-Hodgkin (HH) neuron model. It is very interesting to see that the speedup differs significantly between the two graphs and also the ranking of the four architectures is not the same (i.e. GPU is worst for the Izhikevich model and best for the HH model). The reason is that each architecture has a specific flop/byte (computation/transfer) ratio that makes it most efficient. A CPU core dedicates a lot of chip area to data caching and less to computation. On the other hand a GPU has a huge number of execution units and almost no data caching. The PS3, Opteron and Xeon are somewhere in between. In conclusion, the GPU outperforms the other architectures when the flop/byte ratio is high. This is the case of the HH neuron model that is very computationally demanding (flop/byte = 6.02 [31]). In the case of the Izhikevich model the flop/byte ratio is 0.65 [31] and

so the GPU is outperformed by the other architectures due to lack of caches. Also worth noticing is the fact that when the size of the neural network is very high the speedups obtained by the Xeon and Opteron also drop down and almost equal the speedup of the GPU. This is because the size of the cache becomes insufficient for the size of the network and so the cache's miss rate increases dramatically.

In conclusion a parallel implementation of a spiking neural network is appealing and can achieve substantial improvement of the simulation speed. The simulation performed in this thesis use models that are similar to the Izhikevich model rather than the Hodgkin-Huxley model. Therefore, the GPU implementation is not necessarily the fastest. Nevertheless, it was chosen due to its accessibility and reduced cost. The speedup obtained by the GPU implementation was sufficient to serve all tasks involving this thesis.

## **1.3. Thesis Outline**

The thesis is organized on seven chapters as follows:

- Chapter 2 introduces some basic knowledge about the structure of the biological neuron equipped with dynamic synapses. Several dynamic behaviors are studied and four mathematical models are chosen to be most significant: the integrate and fire neuron, the integrate and fire with adaptation neuron, the integrate and fire with burst neuron, and the resonate and fire neuron. The chapter concludes by presenting some spike coding techniques and the ability of a spiking neuron to act as a context detector and implement a content addressable memory.

- Chapter 3 presents a MATLAB simulation framework that was designed to easily implement and simulate a spiking neural network of desired architecture. The tool also contains functions for result analysis and visualization. The second part of the chapter presents a modification of the framework that allows parallel simulation on several computers connected by a network. The approach proves that the neural network model has a lot of parallelism to be exploited and also offers some improvement in terms of simulation speed. However, the improvement is not satisfactory because of the high communication time between computing units. Consequently, alternative parallel implementations are further searched.

- Chapter 4 presents a parallel implementation that uses a graphics processor to hardware accelerate the simulation. The GPU is designed and optimized to be very efficient on parallel processing and so the implementation of the neural network model is inherently promising. The simulation framework is redesigned such that it suits better the hardware design of the GPU. Throughout the chapter several difficulties are presented and also their solutions. In the second part of the chapter three additional improvements are presented that further accelerate the simulation. The chapter concludes by presenting a benchmark that compares the GPU model to the MATLAB model and also to a C++ model. A communication interface between CUDA C and MATLAB is also provided by means of MATLAB MEX files.

- Chapter 5 presents the Liquid State Machine computing architecture as a

potential solution to information processing using spiking neurons. The chapter

presents the design rules of the network and also its potential advantages and

disadvantages. In the second part of the chapter two alternatives for

implementing the readout units are presented (parallel perceptron and the

multi-layer feedforward network), accompanied by appropriate training

algorithms (p-Delta learning rule and backpropagation). Additionally, three improvements are made to the p-Delta rule that increase the convergence rate and convergence speed.

- Chapter 6 presents an application that uses a Liquid State Machine based on spiking neurons to extract Gabor coefficients from fiducial points of an image. The pre-processing of the input signals is also done by means of spiking neural networks, yielding three variants for the input signal.

- Chapter 7 presents the theoretical and practical contributions brought by the thesis, the conclusions and future work.

# **2. SPIKING NEURAL NETWORKS**

In [1], spiking neural networks (SNN) are presented to be the third generation of neural models. The first generation of neural networks is based on McCulloch-Pitts neurons, also called perceptrons. Interconnecting the neurons in various ways yielded a wide variety of networks like: multi-layer perceptrons, Hopfield Networks, or Bolzmann machines. All networks using perceptrons had a digital output and were useful at classification or modeling digital functions.

The second generation of neural networks uses activation functions in order to obtain a continuously varying output. Some of the most significant networks of this type are: feed-forward sigmoid networks, recurrent networks, and radial basis function networks. This type of networks can model both digital functions and functions with analog input/output. The biological neurons generate spikes rather than analog outputs. However, the second generation of neural networks is biologically plausible assuming that the biological neurons code information using the frequency of the spike train rather than the inter-spike timing relationships. This is present in the higher cortical areas of the brain where neurons adjust their firing rate slowly and so are able to carry frequency information. Another advantage of the continuous activation functions is the possibility to use gradient based training algorithms. Figure 2.1 presents three types of the second generation neural networks.

Fig. 2.1. Second Generation Neural Networks

However, some areas of the cortex perform tasks that require fast computations. In such cases frequency coding is questionable and it is more likely that inter-spike timing is used to encode information [45], [48], [51], [52]. The

#### 20 Spiking Neural Networks - 2

third generation of neural networks tries to accommodate this new requirement. The new model has a "spiking" output that is very similar to the biological neurons. In addition, spiking networks still offer all the features present at the second generation of networks. Figure 2.2 presents the structure of a biological neural network.

Fig. 2.2 Biological Neural Network

The most important parts of a biological neuron are: the neuron cell (the computational unit), the dendrites (the inputs of the neuron), and the axon (the output of the neuron). The bridge between an axon and a dendrite is called synapse. Spikes (also called action potentials) propagate along the axon of the source neuron, cross the synapse and reach the target neuron via its dendrite. When a spike crosses a synapse, the shape, the timing and also the amplitude of the spike is influenced by dynamic properties of the synapse. In reality spikes do not actually cross a synapse. They simply trigger a pre-synaptic mechanism that generates a new post-synaptic spike. Therefore, synapses are active elements. The rest of this chapter presents some physical and chemical mechanisms that are present in biological synapses and neuron cells. It does a mathematical description of the neuron functionality and introduces four simplified models for spiking neurons and dynamic synapses that are suitable for simulation. The models manage to remain simple enough and still capture the main characteristics of the biological neuron. Model simplicity is the key of this project in order to be able to simulate large networks

#### 2.1. Synapses

A synapse is an active functional unit that connects two neurons. Most often it lies at the junction of an axon and a dendrite, but other types of connections are also possible: axon-cell body, axon-axon or dendrite-dendrite. In older neural models synapses are static signal pathways that can only be used at weighing signals, hence the name "static synapses". This simplification comes from the assumption that neural processes are slow and that only firing rates are used at coding information rather than exact spike timing or network dynamics. In reality, the biological synapse, besides being a signal transducer, is a very powerful nonlinear signal pre-processor that has a complex dynamic behavior [50], [53].

#### 2.2. Dynamic Synapses

This sub-paragraph briefly presents the functioning of the biological synapse and introduces a simplified biologically inspired model called dynamic synapse. Figure 2.3 presents the structure of a biological synapse. In the left and right parts of the figure the pre-synaptic axon and the post-synaptic dendrite are depicted. Spikes arriving along the axon of the pre-synaptic neuron are also called action potentials. When an action potential reaches the terminal of the axon it raises the voltage locally causing calcium ion channels to open. This produces an influx of calcium ions that causes the vesicles of neurotransmitters to break and the release the neurotransmitters into the synaptic cleft. On the other side of the synapse, neurotransmitters bind with receptors triggering several ligand-gated ion channels.

Fig 2.3. Biological Synapse

As a result, the membrane potential of the post-synaptic neuron is raised. Eventually, the neurotransmitters brake loose from the receptors causing the channels to close and stopping the increase of the membrane potential. Some of the free neurotransmitters are removed from the synaptic cleft by the reuptake pumps which send them back to the axon terminal. Here the neurotransmitters are repacked into vesicles and are ready to be used again.

The strength of the synapse is considered to be the impact of one presynaptic spike on the membrane potential of the post-synaptic neuron. This is analog to the weight of the static synapse. In contrast with the static synapse, the biological synapse does not have a constant strength, as it varies over time as an effect of several synapse internal mechanisms.

#### 2.2.1. Depressing Synapse

Because neurotransmitters are the triggering factors for post-synaptic potentials they are considered to be the primary resources for this event. The amplitude of the post-synaptic potential depends on several factors like: quantity of released neurotransmitters, number of receptors, and the ability of each activated receptor to produce post-synaptic current. After a pre-synaptic action potential arrives a fraction of the available neurotransmitters are released. If another action potential arrives shortly after the first one, the quantity of available neurotransmitters (resources) might not be as high as for the first one. This is because the synapse did not have enough time to recover from the previous spike.

Equations (2.1), (2.2) and (2.3) model this process. X, Y and Z are functions of time that represent: resources available on the pre-synaptic side (waiting neuro-transmitters), active resources on the post-synaptic side (released neuro-transmitters), and recoverable resources (that can be pumped back to the axon terminal). All variables x, y and z are fractions where 1 represents the maximum level of resources the synapse can provide.

$$\frac{\partial x}{\partial t} = \frac{z}{\tau_{rec}} - x(t_{sp}) U_{SE} \delta(t - t_{sp})$$

(2.1)

$$\frac{\partial y}{\partial t} = -\frac{y}{\tau_{in}} + x(t_{sp})U_{SE}\delta(t-t_{sp})$$

(2.2)

$$\frac{\partial z}{\partial t} = \frac{y}{\tau_{in}} - \frac{z}{\tau_{rec}}$$

(2.3)

Because the shape and energy of the pre-synaptic spike is not important and does not influence the functioning of the synapse or the shape of the postsynaptic potential, it is modeled by a Dirac pulse  $\delta$  that occurs at the time of the spike  $t_{sp}$ . When a spike is received, a fraction  $U_{SE}$  (utilization of synapse efficacy) of the available resources is released (second term of eq. 2.1). At the same time, the same quantity of resources is received on the post-synaptic side (second term of eq. 2.2). As soon as the released resources bind with the receptors the post-synaptic membrane potential starts to increase at a rate proportional to the amount of active resources (eq. 2.4).

$$\frac{\partial V}{\partial t} = A * y(t) \Longrightarrow V(t) = A \int_{0}^{t} y(t) dt$$

(2.4)

Constant A is a scaling constant and represents the static efficacy (weight) of the synapse. The first term of eq. 2.2 represents the rate at which the resourcereceptor binds break apart. The time constant  $\tau_{in}$  controls how fast resources become inactive. All inactive resources are in fact recoverable resources and so Z increases with the same rate (first term of eq. 2.3). The first term of eq. 2.1 and second term of eq. 2.3 show the rate at which resources are recovered (pumped from post-synaptic to pre-synaptic side).

Figure 2.4 presents the dynamic functionality of a biologic synapse and the variation of resource quantities (neurotransmitters) over time. It is considered that the first pre-synaptic spike of the sequence occurs at a moment when all resources have had time to recover and are available for use (x = 1, y = 0, z = 0). It can be noticed that the first spike generates a maximum amount of active resources. This is controlled by the value of  $U_{SE}$ , which in this case is 0.5. The next three spikes have a smaller effect because there is not enough time for the resources to recover. Notice that the resources activated by the  $2^{nd}$ ,  $3^{rd}$  and  $4^{th}$  spikes are similar in amount due to the fact that the period between these spikes is roughly the same. This leads to the conclusion that the efficacy of the dynamic synapse is frequency dependent. Literature shows that this mechanism is present and very useful in biological neural networks because it stabilizes and prevents saturation of the network.

Fig. 2.4. Synapse Dynamic functionality

#### 2.2.2. Synapse Delay

This sub-paragraph introduces a simplification to the synapse model in eq. 2.1, 2.2 and 2.3. As presented in 2.2.1 when a spike is received a certain amount of resources activate. Until these resources inactivate, they produce a current proportional to their amount causing the post-synaptic membrane potential to rise. We simplify the model by considering that resources activate and then inactivate

#### 24 Spiking Neural Networks - 2

instantaneously, reducing  $\tau_{in}$  to zero. Doing so, they trigger their entire associated energy at once, causing the membrane potential to rise as a step function. The simplification causes the membrane potential to rise faster and can potentially lead to a post-synaptic neuron that fires a spike prematurely. In compensation, we introduce a delay between the time when the pre-synaptic spike arrives and the time when the resources activate. This delay is equal to the time the membrane potential would need to rise to the *K* fraction of its final value (eq. 2.5).  $D_0$  is a delay that accounts for all other delays that could potentially appear in a biological neuron (flight time of pre-synaptic spike across the axon length). The model described by equations 2.1, 2.2, 2.3 changes to the model in 2.6, 2.7 and 2.8. *N* is the total number of pre-synaptic spikes.

$$D = -\tau_{in} \ln(1 - K) + D_0$$

(2.5)

$$\frac{\partial x}{\partial t} = \frac{z}{\tau_{rec}} - x(t_{sp}) U_{SE} \delta(t - t_{sp})$$

(2.6)

$$y(t) = U_{SE} \sum_{n=1}^{N} x(t_{spn}) \delta(t - t_{spn} - D)$$

(2.7)

$$\frac{\partial z}{\partial t} = -\frac{z}{\tau_{rec}} + x(t_{sp})U_{SE}\delta(t - t_{sp} - D)$$

(2.8)

#### 2.2.3. Facilitating Synapse

In the previous paragraphs  $U_{SE}$  is constant and controls the amount of resources that become active as the result of a pre-synaptic spike. In reality,  $U_{SE}$  is not constant and is affected by the past activity of the synapse. A model of this mechanism as presented in equation 2.9. When a pre-synaptic spike is received the increased voltage inside the axon terminal causes the calcium channels to open. The fraction of channels that open (out of the total number of available channels) is represented by  $U_{SE}$ . After opening, the channels close at a rate given by  $\tau_{facil}$  (first term in eq.2.9). If a new pre-synaptic spike is received, a fraction  $U_{SE}$  of the closed channels (1 - **u**<sub>SE</sub>) open additionally to the channels that are already open (**u**<sub>SE</sub>). Therefore, the number of channels that open is higher than  $U_{SE}$  and is equivalent to the instantaneous value of  $u_{SE}$ . This type of synapse is called to be facilitating. A spike will increase the efficacy of the synapse if the subsequent spikes arrive in a time window comparable to  $au_{facil}$ . The depressing and facilitating mechanisms are contradictory but have different dynamics and time constants. Therefore, adjusting the  $\tau_{rec}$  and  $\tau_{facil}$  can change significantly the behavior of the dynamic synapse. Additional information about the processing power of synapses can be found in [46] and [49].

$$\frac{\partial u_{SE}}{\partial t} = -\frac{u_{SE}}{\tau_{facil}} + U_{SE} \left(1 - u_{SE}\right) \delta\left(t - t_{sp}\right)$$

(2.9)

#### 2.2.4. Recursive Model for Dynamic Synapse

The dynamic synapse can be modeled globally by a gain *G* and a delay *D*. The synapse is dynamic because the gain is not constant and depends on an internal synapse state  $[x \ u_{SE}]$ . At each moment the gain is controlled by the state variable as shown in equation 2.10. Superscript index *n* is a discrete time index associated with the *n*<sup>th</sup> pre-synaptic spike.

$$G^{n} = A * u_{SE}^{n} * x^{n}$$

(2.10)

Equations 2.6 and 2.9 can be transformed from differential into recursive expressions that allows us to compute the state variable at the time of the  $(n+1)^{th}$  spike based on the state variable at the time of the  $n^{th}$  spike. Equation 2.11 describes the computation of  $x^{n+1}$  based on  $x^n$  and  $u_{SE}^n$ .  $\Delta t_n^{n+1}$  is the time interval between the consecutive pre-synaptic spikes. In a similar way equation 2.9 can be rewritten as a recursive expression in 2.12, where  $U_{SE}$  is the utilization of synaptic efficacy in static conditions (low frequency spike trains compared to  $1/\tau_{facil}$ ).

$$x^{n+1} - x^{n} = -\underbrace{x^{n}u_{SE}^{n}}_{activated} + \underbrace{\left(1 - x^{n} + x^{n}u_{SE}^{n}\right)\left(1 - \exp\frac{-\Delta t_{n}^{n+1}}{\tau_{rec}}\right)}_{re \operatorname{cov}ered} \Longrightarrow$$

$$x^{n+1} = 1 + \left(x^{n} - x^{n}u_{SE}^{n} - 1\right)\exp\frac{-\Delta t_{n}^{n+1}}{\tau_{rec}} \tag{2.11}$$

$$u_{SE}^{n+1} = U_{SE} + u_{SE}^{n} (1 - U_{SE}) \exp \frac{-\Delta t_{n}^{n+1}}{\tau_{facil}}$$

(2.12)

A useful property of the above model is that whenever the pre-synaptic spike train has a steady frequency, the synapse state [x  $u_{SE}$ ] stabilizes at a constant value that is dependent on the frequency of the spike train. This is a useful property that is used in the following chapters at building the spiking neural network simulation framework. Equations 2.13 and 2.14 compute the synapse state when the frequency of the spike train is steady and equal to  $f_{sp}$ .

$$x = \frac{1 - \exp \frac{-1}{f_{sp} \tau_{rec}}}{1 - (1 - u_{SE}) \exp \frac{-1}{f_{sp} \tau_{rec}}}$$

(2.13)

$$u_{SE} = \frac{U_{SE}}{1 - (1 - U_{SE}) \exp \frac{-1}{f_{sp} \tau_{facil}}}$$

(2.14)

### **2.3. Spiking Neurons Models**

Synapses transmit action potentials between pairs of neurons. When a neuron receives a post-synaptic spike its membrane potential is changed and in some cases the neuron generates an action potential. There are several models that simulate the mechanisms governing the functioning of a neuron cell. The most elaborate model is the Hodgkin-Huxley neuron which was developed after studying the giant squid neuron. Due to limited computing resources, several other simplified models have been later developed. These models try to preserve the aspects of neuron functionality that are believed to be significant to information processing. This thesis presents and uses four different models for spiking neurons. In order to justify the simplified models the next sub-paragraph introduces the functionality of the biological neuron as presented by Hodgkin-Huxley.

#### 2.3. 1. The Biological Neuron

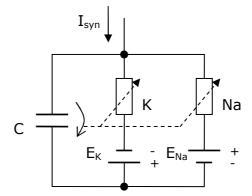

Like all cells the neuron has a cell membrane that separates it from the extra-cellular space. The interior of the cell is connected to the exterior by a series of ion pumps and voltage-controlled ion channels. Sodium, potassium and calcium ions are most important in the functioning of the neuron. The active pumps create a flux of ions between the interior and exterior of the neuron cell, thus creating a difference in ion concentration. Sodium is pumped out of the cell while potassium is pumped into the cell. The difference in concentration produces a voltage across the cell membrane called Nernst potential. This voltage opens the voltage-controlled ion channels and produces a flux of ions that is opposite to the pump flux, thus balancing the process. If only sodium was present the equilibrium is at about +50mV across the cell membrane. In the case of potassium equilibrium sets in at around -77mV. With both types of ions present, the equilibrium potential was experimentally determined around -65mV. At this voltage, sodium ions flow into the cell while potassium ion flow out of the cell (via the ion channels). On the other side, the ion pumps balance the process by pumping the ions back. The equilibrium voltage is called resting potential. This is the potential across the neuron membrane if the neuron is not disturbed by an external stimulus for a sufficiently long period of time. Figure 2.5 presents the Hodgkin-Huxley neuron model. The capacitor represents the neuron membrane that serves as an insulator between the inside and outside of the neuron cell. The two batteries represent the equilibrium potentials generated by the sodium and potassium ion flows. The ion channels are modeled by variable resistors that are controlled by the voltage across the membrane. The circuit is stimulated by an external current that represents the post-synaptic current.

Despite its apparent simplicity the model can have a very complex behavior. This is because the dependence of the channel conductance on the membrane potential is very dynamic and highly non-linear. Furthermore, combining two or more channels with different parameters can lead vast range of dynamic behaviors for the neuron model. Equation 2.15 describes the functionality of the model, where the sum is across all existing ion channels (Na and K in this case). Equation 2.16 sums the components of the sodium and potassium currents respectively.  $G_n$  is the maximum conductance of the channel. This conductance is modulated by the dynamic variables m and h which are called activating and inactivating variables. Parameters p and q are constants and are specific to the ion channel. In the case of

the Hodgkin-Huxley neuron the parameters were experimentally determined ( $p_{Na}=3$ ,  $q_{Na}=1$ ,  $p_{K}=4$ ,  $q_{K}=0$ ). Because  $q_{K}$  is zero the potassium channel has no inactivation variable.

Fig. 2.5 Hodgkin-Huxley Neuron Model

$$C\frac{\partial u}{\partial t} = -\sum_{n} I_{n}(t) + I_{syn}(t)$$

(2.15)

$$I_{Na} + I_{K} = g_{Na} m_{Na}^{p_{Na}} h_{Na}^{q_{Na}} (u - E_{Na}) + g_{K} m_{K}^{p_{K}} h_{K}^{q_{K}} (u - E_{K})$$

(2.16)

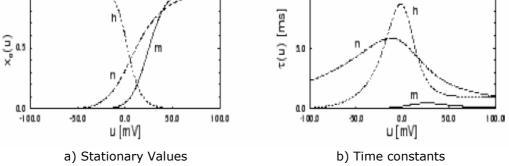

The activation and inactivation variables m and h are voltage dependent and also time dependent, therefore they have a dynamic behavior. Figure 2.6 shows an example of how these variables behave. The left picture represents the static value of the variable. The right picture shows the time constant of the variable.

$$\partial t = \tau(u) \left( u = u_0(u) \right)$$

$$\frac{\partial x}{\partial t} = -\frac{1}{\tau(u)} \left( x - x_0(u) \right) \tag{2.17}$$

1.0

Fig. 2.6 Activation and inactivation variables

#### 28 Spiking Neural Networks - 2

During the transitory regime, variable x changes asymptotically towards the new stationary value  $x_0(u)$  with time constant  $\tau(u)$  (eq.2.17). Note that both the stationary value and the time constant are voltage dependent. It is important to notice that the m and h variables model biological mechanisms that activate and deactivate the ion channels independently. Therefore, the variables are also independent; they can change with different time constants; and their effect is multiplicative since any of the variables can annihilate the effect of the other.

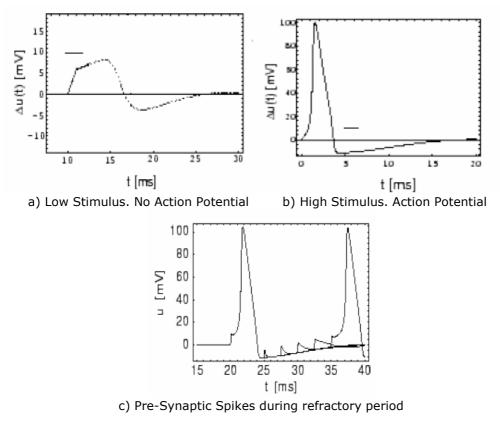

#### 2.3.1.1. Spike Generation

When no external stimulus is present the neuron settles at resting potential. This means that the activating and inactivating variables have just the right value to keep the Na and K ion channels open at the levels required for equilibrium. If an external synaptic current is injected the potential across the membrane potential rises. As an effect all variables *m* and *h* also rise for both Na and K. Notice that the activating variable  $m_{Na}$  of the Na channel has a time constant that is significantly smaller than the rest. This means that this variable will rise a lot faster that the other. It also means that the Na ion channel will open first allowing an influx of Na ions inside the cell. This causes an additional increase in membrane potential which in turn opens the Na channel even more. Therefore, a temporary positive feedback appears.

If the external stimulus is weak and initial increase in membrane potential is also small. This places the  $m_{Na}$  variable at a position on the graph where the sensitivity of the variable is small with respect to voltage variations. Consequently, the positive feedback created by the Na channel is small and is unable to destabilize the neuron. This corresponds to the situation presented in figure 2.7a. Having larger time constants it takes some time until the inactivating variable  $h_{Na}$  of the Na channel and the activating variable  $m_K$  of the K channel rise. However, when that happens two effects can be seen. First, the Na channel is closed by its inactivating variable. Second, the K channel is opened producing an ex-flux of K ions out of the cell. This produces a decrease in the membrane potential. Because of the high time constant of the K channel there is a certain delay until the channel manages to close. This creates a negative overshoot of membrane potential.

If the external stimulus is strong it will produce a higher membrane potential and will bring the Na channel in a state where it is more sensitive to potential variations (upper part of the graph). This creates a stronger positive feedback. If the membrane potential is sufficiently high (reaches a threshold), the positive feedback is sufficiently large to sustain itself. This opens the Na channel to maximum allowing a massive in-flux on Na ions inside the neuron and leading to the generation of an action potential. This is shown in figure 2.7b. At such high values of the membrane potential the time constants of the  $h_{Na}$  and  $m_K$  decrease significantly allowing quick inactivation on the Na channel and activation of the K channel. The high value of the membrane potential is not generated. The result is a significantly stronger negative overshoot called refractory period.

#### 2.3.1.2. Refractory Period

During the refractory period the neuron is less sensitive to incoming stimuli. This means that a stimulus that would generate an action potential if the neuron is in resting state might not generate an action potential if the neuron is in refractory state. The effect of a refractory period is not just a shift towards a more negative potential (an increased distance to the threshold). In addition, during the refractory period the overall conductance of the neuron membrane is reduced because very many ion channels are opened immediately after the action potential. This increased conductance allows the charge that is brought by the external stimulus to drain quickly and so diminishes the impact of the stimulus upon the membrane potential during the succeeding time window. This is depicted in figure 2.7c. There is a sequence of four spikes during the refractory period following the action potential. All spikes carry the same amount of energy and raise the membrane potential equally. However, the potential brought by the first spike diminishes a lot faster than the potential brought by the following spikes. This is because the refractory effect is more profound then. During the refractory period the chance that a group of spikes triggers an action potential is reduced. The same group of spikes might easily trigger an action potential if the neuron was at resting potential. In addition, if the group of spikes merged into a single spike that carries the cumulated energy it might trigger an action potential even if the neuron is in refractory period.

Fig. 2.7. Functioning of the Neuron. Generating spikes

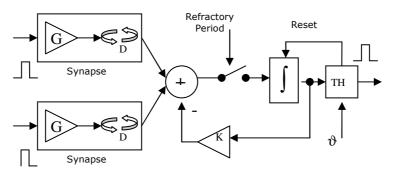

#### 2.3. 2. Integrate and Fire Neuron

The integrate-and-fire neuron model (I&F) is the simplest model inspired from the Hodgkin-Huxley neuron. The I&F neuron is shown in figure 2.8 and is modeled by equation 2.18 or 2.19 (differential form). The synapses are constructed

#### 30 Spiking Neural Networks - 2

from a gain block and a delay block. The gain block is either a simple constant gain or can be built as a state machine modeled by equation 2.10, 2.11 and 2.12. It can be seen that the neuron cell is represented by a lossy integrator which is the equivalent of the capacitor. The resting potential of the neuron is zero. All postsynaptic spikes are added and accumulated by the integrator as membrane potential. If the potential reaches threshold  $\vartheta$  the integrator resets to its resting potential and an action potential is generated at the output. If the threshold is not reached and no new post-synaptic spikes arrive the integrator leaks to its resting potential with loss factor K. Two possibilities are proposed for modeling the refractory period. In figure 2.8 it is implemented by a switch controlled by a timing circuit. This prevents the neuron to accumulate any potential during the refractory period and so no new action potentials can be generated during this period.

Another method would be to reset the integrator at a value lower than its resting potential. This approach is similar to what the biological neuron does, and decreases the probability that a new action potential is generated during the refractory period. However, this model is linear while the biological neuron is highly non-linear and has a significantly higher probability to generate a new action potential during the refractory period. For this reason and also from experimental results the discontinuous switch controlled model (fig. 2.8) is preferred.

Fig. 2.8. Integrate and fire neuron model

$$p_{i}(t) = \int_{i}^{t} \sum_{k=1}^{K} G_{ik} * u_{i}(t - D_{ik}) - k \_loss * p_{i}(t) \qquad p_{i}(t) \le Th \qquad (2.18)$$

$$p_{i}(t) = 0, \ ti = t \qquad p_{i}(t) \ge Th$$

$$\frac{\partial p_i(t)}{\partial t} = I_{syn} - k \, loss * p_i(t)$$

(2.19)

The leakage current models the effect produced by the potassium currents which tend to bring the neuron at resting potential if the post-synaptic stimulus is not sufficient to trigger an action potential. The main advantage of this model is its simplicity, requiring a reduced number of floating-point operations for simulating one neuron. This advantage can be important if very large networks need to be simulated. As a tradeoff, the model does not have adaptation or bursting abilities.

#### 2.3.3. Integrate and Fire with Burst Neuron

A burst is a sequence of action potentials generated at very short time intervals. The first action potential is triggered by the same mechanisms of a nonbursting neuron. The remaining spikes of the sequences are triggered by a selfsustained mechanism and do not need any synaptic stimulus. The biological explanation for such functionality stands in the existence of the calcium ion channel which was mentioned in paragraph 2.3.1. Like the sodium current, the calcium current is also from the outside towards the inside of the neuron cell, thus raises the membrane potential. The mathematical model of the calcium current is given by equation 2.16 and so is the same as that of sodium or potassium. Additionally, the shape of the activating and inactivating variables m and h is also similar. The distinctive characteristic of the calcium ion current is that the curves of the activating and inactivating variables are shifted left towards the negative area of the membrane potential. This is the reason why this current is also called "low-threshold calcium current". At resting potential the  $m_{Ca}$  variable is fully activated while the  $h_{Ca}$ variable is fully inactivated. Therefore, the calcium channel is closed as an effect of the  $h_{Ca}$  variable. The sodium channel is also closed at resting potential as an effect of the  $m_{Na}$  variable. Even if the sodium channel and calcium channel are in the same state, closed, each has a different reason for it: the sodium channel is not-activated, while the calcium channel is in-activated. If for any reason the membrane potential decreases below the resting potential the inactivating variable  $h_{Ca}$  will start to rise and the calcium channel will open. The membrane potential can go below the resting potential either as the result of an inhibitory synaptic current or an afterspike negative overshoot (due to potassium currents).

Figure 2.9 shows an example the neuron is stimulated with an inhibitory synaptic current. The inhibitory current is removed (at time 600ms) the membrane potential starts to increase,  $m_{Ca}$  starts to increase and  $h_{Ca}$  starts to decrease. Because  $h_{Ca}$  has a large time constant and does not decrease immediately the activating variable  $m_{Ca}$  opens the calcium channel. As a result the membrane potential is increases and might cause a sodium channel to open and generate an action potential. After the first action potential, if the  $h_{Ca}$  still has not had time to decrease, the calcium current is still on and causes a new action potential. Several such action potentials can be generated in a burst. The number of action potentials is given by the time window allowed by the time constant of the  $h_{Ca}$  variable. Once the calcium channel closes the mechanism cannot be triggered until the membrane potential is again sufficiently low.

The I&FB neuron is a simplified model that tries to capture the functionality described above. Equations 2.20 and 2.21 implement the model. The first two terms of eq.2.20 are the same as for the I&F neuron. Additionally, there is a third term related to the calcium current. The term  $p_{Ca}$  is smaller than the resting potential and sets the potential level where the calcium channel starts to open ( $m_{Ca}$  and  $h_{Ca}$  curves cross). Equation 2.21 shows that whenever the potential is below  $p_{Ca}$  the calcium current increases and when the potential is above  $p_{Ca}$  the calcium current decreases. In the case of the biological neuron, both the *m* and *h* variables influence the calcium current increases as effect of the *m* variable and that the current decreases as effect of the *h* variable. Consequently, the  $\tau_m$  time constant controls the rate at

which the calcium current increases while the  $\tau_h$  controls the rate at which the current decreases.

Fig. 2.9. Calcium Current Effect

Function *H* of eq. 2.20 is the Heaviside function. Its purpose is to disable the calcium current when the potential is below  $p_{Ca}$ . In the case of the biological neuron a membrane potential below  $p_{Ca}$  prepares the calcium channel to open by raising the level of  $h_{Ca}$ . However, the channel is closed because of the  $m_{Ca}$  variable and remains so until the membrane potential is above  $p_{Ca}$ . Because in a similar situation the model described in eq. 2.20 and 2.21 has an increasing current, the current needs to be shunted artificially until the membrane potential is above  $p_{Ca}$ . This is achieved by the *H* function.

The calcium current influences the neuron at small potentials above the resting potential. It generally helps at producing sodium current and does not trigger the action potential itself. For this purpose, the calcium current term in eq. 2.20 is modulated by a term that represents the distance between the membrane potential and the reference potential  $p_{T}$ .

$$\frac{\partial p}{\partial t} = I_{syn} - Kp + I_{Ca}H(p - p_{Ca})(p_T - p)$$

(2.20)

$$\frac{\partial I_{Ca}}{\partial t} = \begin{cases} -I_{Ca}^{\max} \frac{I_{Ca}}{\tau_h}, p > p_{Ca} \\ \frac{I_{Ca}^{\max} - I_{Ca}}{\tau_m}, p < p_{Ca} \end{cases}$$

(2.21)

If parameter  $p_{Ca}$  is set at a level that is reached by the membrane potential during the refractory period and also if parameters  $I_{Ca}^{max}$  and  $\tau_m$  are sufficiently large, any sodium generated action potential can trigger a burst. For this case the refractory period cannot be modeled by a switched as described in 2.3.2. The duration of the burst can be controlled by parameter  $\tau_h$ .

#### 2.3. 4. Integrate and Fire with Adaptation Neuron

Adaptation is a neuron property to adjust its sensitivity to incoming stimulus in order to prevent over excitation and output saturation. The biological neuron is able to adapt by combining two special ion currents. The first current is called "highthreshold calcium current". This current is very similar to the low-threshold calcium current presented in the previous paragraph. The difference is that this current activates only at high values of the membrane potential, particularly during the generation of action potentials. The high threshold calcium current has two roles: firstly, it produces an additional boost to the membrane potential during the action potential; secondly, and more important for the adaptation mechanism, it temporarily increases the calcium concentration inside the neuron cell immediately after the action potential.

In addition, a new type of potassium current is present. It differs from the regular K currents by the fact that it flows through a calcium dependent-voltage independent potassium channel. Consequently, this channel opens when the calcium concentration is high regardless of the potential across the neuron membrane. This dependence law is shown in equation 2.22, where  $Ca^{2+}$  is the calcium concentration and c is a parameter.

$$\frac{\partial m}{\partial t} = \alpha m - \beta (1 - m), \alpha = \min(c [Ca^{2+}], 0.01), \beta = 0.001$$

(2.22)

If an isolated action potential occurs the calcium concentration rises but the calcium dependent potassium channel does not have sufficient time to open. On the other hand, figure 2.10b shows that whenever several action potentials occur during a short interval of time, the persistent high calcium concentration allow the potassium channels to open. As a result, the outward potassium current acts as an inhibition current. Figure 2.10a shows that the frequency of action potentials decreases even if the input stimulus is constant, exhibiting a mechanism of adaptation against over stimulation.

activation variable of potassium channel

Fig. 2.10. Adaptation Mechanism

$$\frac{\partial p}{\partial t} = I_{syn} - Kp + I_K^{Ca} \left( p_K^{Ca} - p \right)$$

(2.23)

$$\frac{\partial I_{K}^{Ca}}{\partial t} = \frac{I_{K}^{\max} \delta(t_{spk}) - I_{K}^{Ca}}{\tau_{K}^{Ca}}$$

(2.24)

#### 2.3. 5. Resonate and Fire Neuron

Resonate and fire (R&F) neurons exhibit sub-threshold oscillations when an action potential is not generated. This type of behavior makes the neuron sensitive to the exact timing of the pre-synaptic spikes and therefore requires an excitatory spike train that resonates with its internal frequency in order to generate an action potential. Many biological neurons also exhibit such behaviors. To explain such functionality we return to the biological model containing a sodium channel and a potassium channel. When the neuron is stimulated the sodium channel opens and the membrane potential rises. If the increase is not enough to trigger an action potential, the sodium channel inactivates and the potassium channel opens causing the membrane potential to decrease. However, the membrane potential does not decrease to the same extent as it would in the case of an action potential. The low potential inactivates the potassium channel and "de-inactivates" the sodium channel causing the membrane potential to rise again. After a few such damped oscillations the membrane comes to a stop at the resting potential. When an action potential is generated, the low membrane potential during the refractory period shuts down the sodium channel completely and so an oscillation does not occur.

The easiest way to model an R&F neuron is to represent the membrane potential as a complex number p, where the real part is the current component and the imaginary part is the voltage component. Equation 2.25 models the variations of membrane potential for an R&F neuron. Parameter b is negative and represents the attraction to the rest state.  $\omega$  is the internal frequency of the neuron. Parameter a is introduced to modulate the amplitude and phase of the synaptic current. However, in most cases it is a real number and therefore cannot shift the phase of the membrane potential.

$$\frac{\partial p}{\partial t} = aI_{syn} + (b + j\omega)p \qquad \text{Im}(p) < Th \qquad (2.25)$$

$$p = jTh \text{ or } p = 0 \qquad \text{Im}(p) \ge Th$$

(2.26)

Whenever the voltage component (Im(p)) exceeds the threshold the membrane potential is brought back to an initial reset state and the neuron output generates an action potential. The reset state is either zero, which is analog to the resting state of the previous models, or can be any complex number (i.e. *jTh*). In the latter case the neuron continues to oscillate starting from the amplitude and phase given by the reset state.

Figure 2.11 plots the membrane potential of a R&F neuron when it is stimulated with four different spike trains. In 2.11a the three spikes are grouped and arrive within a short interval of time. This boosts the membrane potential above the threshold and triggers an output action potential. The action potential is represented by the solid round marker. In this case the reset state is  $j^*TH$ .

In 2.11b the spikes are out of phase relative to the oscillation of the membrane potential. It can be seen that the third input spike actually lowers the amplitude of the oscillation and therefore diminishes the probability of an action potential. In 2.11c the third input spike has a timing that is not close together with the first and second spike. Even so, because the timing of the third spike has roughly the same phase relative to the phase of the oscillation an action potential is generated. In figure 2.11d the second spike is out of phase with the other spikes. However, because the spike is inhibitory, it is able to trigger an action potential.

Additional information about neuron models can be found in [47]

Fig. 2.11. R&F Neuron Membrane Potential

### 2.4. Coding with Spikes

One of the most difficult problems involving processing with neural networks is finding an efficient method to represent and code information. Several approaches have been tried each of them having advantages and disadvantages [32], [34]. For example, some neural network models use a continuous variable as output even though the biological counterpart generates spikes. This approach is based on the assumption that the information is coded entirely in the rate of the spike train. Hence, time-averaging along the signal reduces it to a continuous variable.