# POWER FACTOR CORRECTION USING BL-CSC CONVERTER FOR BLDC MOTOR DRIVE

S.KALIAPPAN Kumaraguru College of Technology, Coimbatore, Tamil Nadu, India. kalies.me@gmail.com +91 9789700655

Abstract: This paper presents a Power Factor Correction (PFC) based Bridge less Canonical Switching Cell (BL-CSC) converter-fed Brushless DC (BLDC) motor drive. The BL-CSC converter works in a discontinuous inductor current mode in order to obtain a 0.99 power factor of operation. The speed control of the BLDC motor is achieved by adjusting the DC bus voltage using a PI controller. Voltage Source Inverter (VSI) is operated at the fundamental frequency for reducing the switching losses of BLDC motor electronic commutation. By the partial elimination of the diode Bridge rectifier at the front end the bridgeless configuration of CSC converter has low conduction losses. The proposed configuration is validated using a MATLAB simulation and laboratory experimental setup, which shows a considerable increase in the efficiency.

Key words: BLDC Motor, VSI, CSC, BL-CSC, sensor-less, diode bridge rectifier.

#### 1. Introduction

Brushless DC (BLDC) motors are suggested for many medium and low power drives applications due to their following characteristics such as high flux density per unit volume, high efficiency, low maintenance requirement, reduced Electromagnetic Interference (EMI), ruggedness, and an extensive range of speed control [1][7][10].

BLDC motors [2] have applications in many areas such as household appliances, transportation (hybrid vehicle) aerospace heating, ventilation and air conditioning system, motion control and robotics, renewable energy, etc.

The BLDC motor is an AC motor with dc characteristics consisting of three-phase concentrated stator windings and a permanent magnet rotor. As the BLDC motor does not have any mechanical brushes and commutator assembly the wear and tear of the brushes and sparking issues are eliminated in BLDC motor [3][17].

# **R.RAJESWARI**

Department of EEE, Government College of Technology, Coimbatore, Tamil Nadu, India rreee@gct.ac.in +91 9944959905

Conventionally BLDC drive is fed by an uncontrolled rectifier through a DC link capacitor followed by a three-phase Pulse Width Modulation (PWM)-based VSI [4][18]. The diode bridge rectifier draws harmonic-rich current from the supply and leads to very low power factor at AC supply [5][14]. The total harmonic distortion THD of the supply current is above 10% and poor power factor ranges around 0.72, which is not accepted by IEC 61000-3-2. These THD and power factor problem can be reduced by the variable DC-link voltage based speed control of BLDC motor, here the VSI is utilized to operate in low switching frequency. Variable DC-link voltage is obtained by the SEPIC AND CUK converter at the front end of the VSI feeding BLDC motor using a variable voltage control using two current sensors [6][19].

The front SEPIC and CUK converter helps in the reduction of drawing the harmonic current from the source and improves the power factor up to 0.9. Selection of operating mode of the front-end converter plays an important role between the stresses on PFC switches and the cost of the overall system [8]. Designed front-end converter operates in two different modes such as Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM), was a voltage follower approach is considered as one of the control schemes for PFC converter at DCM mode [7][13].

BL-CSC converter is operated in Discontinuous Inductor Current Mode (DICM) were the inductor  $l_1 \& l_2$  current is discontinuous, on the other hand, the voltage across the capacitors  $C_1\& C_2$  are continuous [8]. An approach of variable DC link voltage based speed control of the BLDC motor is used and implemented by electronic commutation with reduced switching losses in the VSI [9]. PI control is employed in DC Link voltage control with its optimized  $k_p$  and  $k_i$ constants by using GENETIC ALGORITHM optimization.

## 2. BLDC Motor Drive

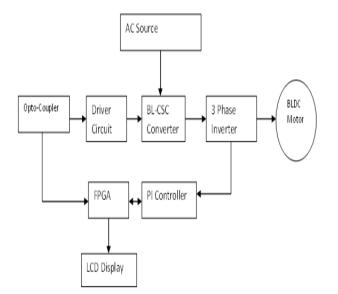

System configurations of the proposed BLDCM drive are shown in Fig. (1), the system comprises of a Diode Bridge Rectifier (DBR), PFC-CSC converter and a three-phase VSI connected to the BLDCM. A sensorless control of BLDCM is used in order to eliminate the rotor position sensors for electronic commutation [1] [11].

Speed control of BLDCM over a wide range is achieved by varying the voltage at DC bus of VSI. The VSI feeding the BLDCM is operated at a fundamental switching frequency to obtain electronic commutation at minimal switching losses [12].

Diode bridge Rectifier (DBR), converts AC signal to DC signal, a dc filter is placed next to reduce the harmonics from the DBR. The Bridgeless Canonical Switching Cell (BL-CSC) is introduced in order to reduce the usage of diodes, thereby reducing the harmonics generated by the diode bridge rectifier. From BL-CSC converter, the BLDC motor is fed through voltage source inverter and the motor rotates. The PI controller is used to find the controlling signal with respect to the error signal and driver units are used generate trigger pulse, s for the voltage source inverter using the control signal got from the PI controller. The FPGA controller has the voltage of minimum 5v, so driver unit is used for the purpose of optical isolation between the FPGA board and the inverter circuits.

Fig. 1 Block Diagram of the proposed system

#### A. Bridgeless Rectifier and Boost Converter

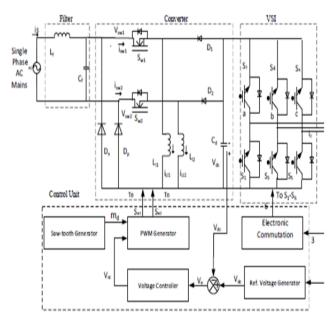

Fig. 2 shows the circuit diagram of the PFC with bridgeless rectifier with the BL-CSC converter. Two buck converters connected in a parallel input series output manner comprises the bridgeless rectifier whose output is given to a boost converter to get improved power factor. The upper buck converter comprises of switch S1 and diode D1, freewheeling diode D3, and inductor L1 and capacitor C1 conducts during the positive half cycle and the lower buck converter comprises of switch S2 and diode D2, freewheeling diode D4 and inductor L2 and capacitor C2 operates during the negative half cycle. On the other hand, the boost converter consists of inductor L3, switch S3, diode D5 and capacitor C0.

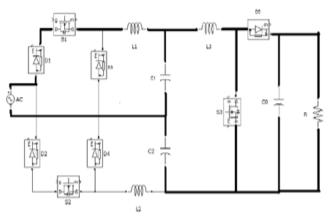

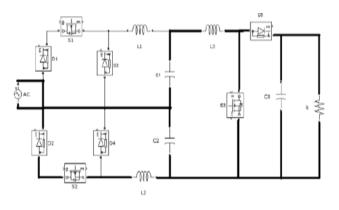

During the positive half cycle, the upper buck converter of the bridge rectifier consists of diode D1, switch S1 inductor L1, capacitor C1, freewheeling diode D3, and the boost converter consists of inductor L3, Diode D5, switch S3 and capacitor C0 operates. While the switch S1 is on inductor L2 stores energy and when S1 is off the stored energy in inductor L2 freewheel through the diode D3, during the above said operation voltage develops across the capacitor C1 is fed as input to the boost converter Vin. Fig. 3 and Fig. 4 depicts the operation of the circuit during the line voltage at positive and negative half cycle.

Fig. 2 Topology of the Novel Three-Phase Bridgeless BL-CSC Converter

Fig. 3 Operation of the Circuit during the Period when Line Voltage is Positive

Fig. 4 Operation of the Circuit during the Period When Line Voltage Is Negative

Each phase of the three-phase bridgeless boost PFC are capable of working independently, during the positive and negative semi-cycles of the AC input, the circuit of A-phase is equivalent to an arrangement of two boosts PFC circuits with opposite voltage.

#### **3. DESIGN PROCEDURE**

Phase-delay (phase-lag) generated by sensing circuitry and a hysteresis comparator is compensated by phase lead compensator. The phase delay occurs between the virtual Hall signals and the actual zero crossing of the line back-EMF measured.

Phase-delay of 17-18 is got at the rated speed, the phase-lead compensator is designed using the transfer function in Eqn. (1),

$$G_{c}(S) = a\left(\frac{a(s+\omega_{c1})}{(s+\omega_{c2})}\right) = a\left(\frac{(s+1)/aT}{(s+1)/T}\right)$$

(1)

Where the  $\omega_{c1}$  and  $\omega_{c2}$  are the two corner frequencies, constants a and T is the time constant shown in Eqn.

(2),

$$a = \frac{(1+\sin(\varphi_m))}{(1-\sin(\varphi_m))}; \ T = \frac{1}{(\omega_m\sqrt{a})}$$

(2)

where  $\phi_m$  is the required phase lead angle and  $\omega_m$  is the frequency analogous to the maximum phase lead angle ( $\phi_m$ ). In addition,  $\omega_m$  can also be represented as Eqn. (3),

$$Log_{10}(\omega_m) = \frac{1}{2} \{ log_{10}(\omega_{c1}) + log_{10}(\omega_{c2}) \}$$

(3)

The value of constant 'a' is determined using Eqn. (2) as 1.8944 and the time constant, T is calculated as 1.44x10<sup>-3</sup> rad/sec using Eqn. (3). Two corner frequencies,  $\omega c1$  and  $\omega c2$  are obtained as  $\omega_{c1} = 1/T = 692$  rad/sec and  $\omega_{c2} = 1/(aT) = 365$  rad/sec. In order to obtain a maximum phase shift of 18°at rated speed, subsequently to the frequency of 80 Hz (i.e.  $\omega_m \approx 503$  rad/sec), By substituting the above-said values in Eqn. (1), the transfer function of the required phase lead compensator as Eqn. (4) can be got,

$$G_{c}(s) = 1.8944 \ \left(\frac{(s+365)}{s+692}\right) \tag{4}$$

$$G_{c}(s) = \frac{\left(s + \left(\frac{1}{R_{a}C_{a}}\right)\right)}{\left(s + \left(\frac{1}{R_{a}C_{a}}\right) + \left(\frac{1}{R_{b}C_{a}}\right)\right)}$$

(5)

thereby equating the Eqn. (5), the value of  $R_a$  and  $R_b$  are calculated as 27.4 k $\Omega$  and 30.6 k $\Omega$  (Ca = 0.1  $\mu$ F).

## 4. SOFTWARE RESULTS

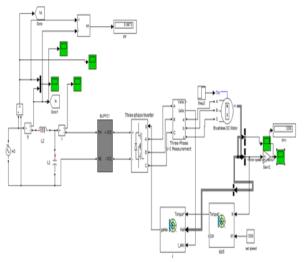

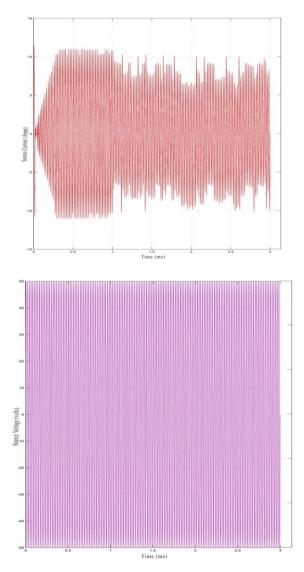

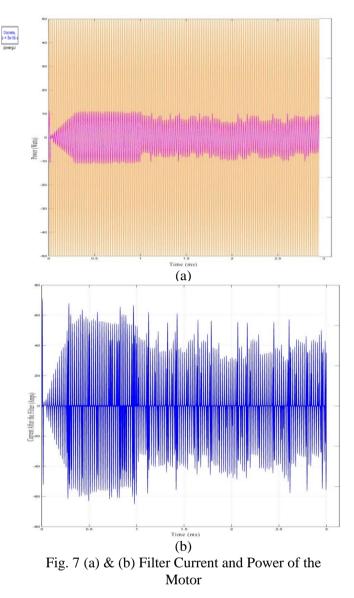

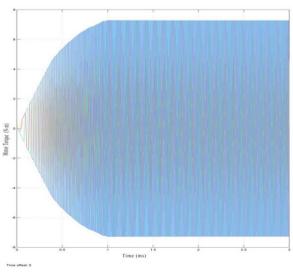

The simulation diagram of the BL-CSC converter-fed BLDC motor drive is shown in Fig.5. The input Voltage and current are shown in figure 6. The filtered current and power are shown in figure 7. The motor speed and torque developed is shown in figure 8. Table 1 shows the evaluation parameters.

Table 1. List of Parameters

| Input Voltage       | 50 V                              |

|---------------------|-----------------------------------|

| Filter (LC)         | L= $1.5e^{-3}$ and C= $330e^{-9}$ |

| Switching Frequency | 50 Hz                             |

| Motor               | 3 Phase BLDC                      |

| Set Speed           | 1200 rpm                          |

| Reference Speed     | 2000 rpm                          |

Fig. 5 MATLAB Simulation Diagram

Fig 6. Source Current and Voltage

(a)

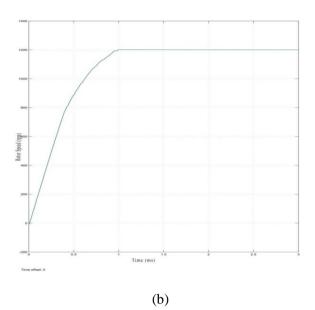

Fig. 8 (a) & (b) Motor Torque and Speed of the

Rotor

AHMY\_SP6\_LX9\_LC FPGA board is used due to it's a low-cost board featuring Xilinx Spartan-6 FPGA. It is

Hardware Results

(b)

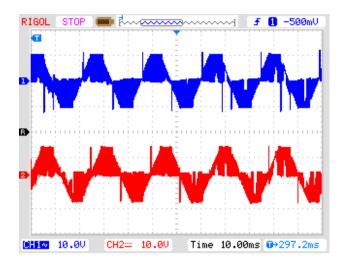

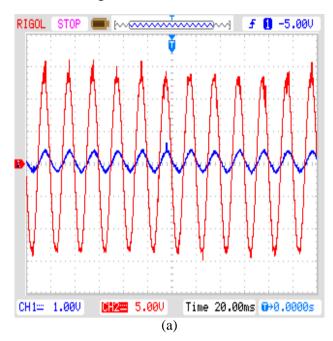

Fig. 9 (a) & (b) Current and Voltage of the BLDC Motor

specially designed FPGA board for research, experimentation and learning system. The TOSHIBA

**A**.

TLP250 consists of a GaAlAs light emitting diode and an integrated photodetector is used as an optocoupler. This unit is 8–lead DIP package.TLP250 provides isolation and gate driving circuit of IGBT or power MOSFET.

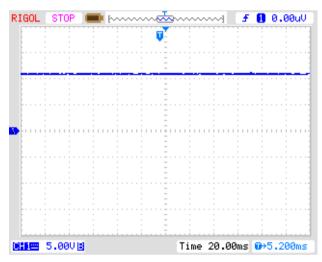

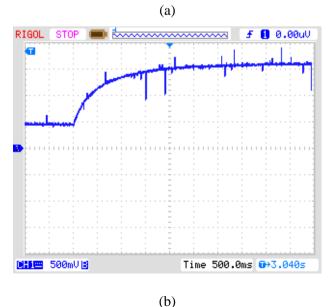

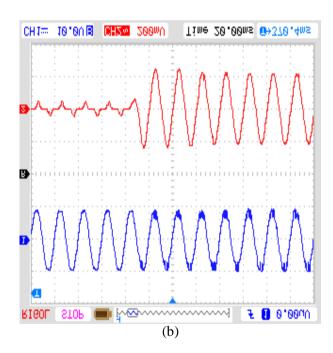

Fig. 10 (a) & (b) DC Link Voltage and Transient Voltage Waveform

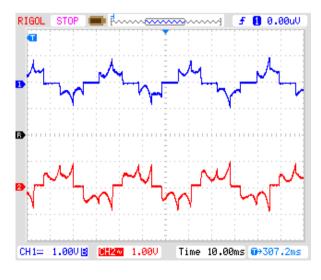

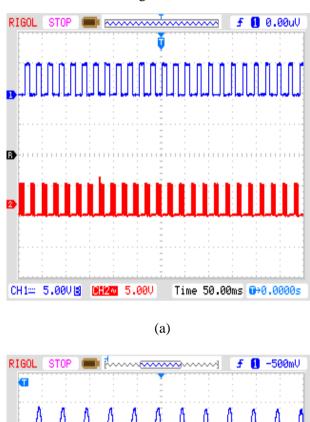

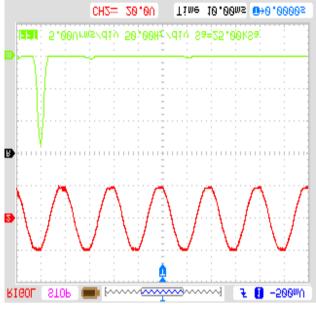

(b) Fig. 11 (a) & (b) PWM Pulses and Inductor Current & Source Current before Converter ON

Time 10.00ms 0→600.0ms

082 500mV

B

CH1~ 500mV

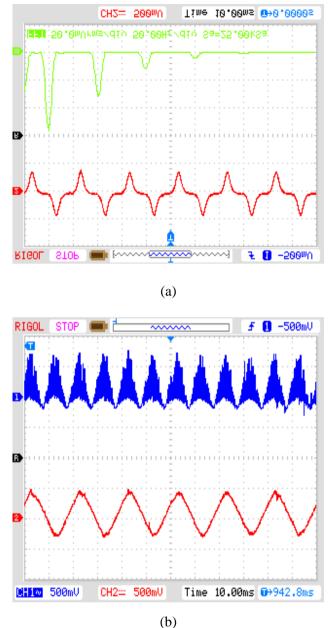

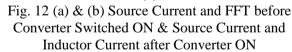

The BLDC motor stator voltage and current are as shown in Fig. 9.The DC link voltage and its transient are shown in Fig. 10. The inductor current and source current before converter ON state waveform and the converter PWM signal is as shown in Fig. 11. Source current and FFT before converter switched ON state waveform and source current and FFT, after converter switched ON state waveform, is as shown in Fig. 12. Source voltage and current after converter ON state and source voltage and current transient are as shown in Fig. 13. The Source voltage and corresponding FFT is as shown in Fig. 14.

Fig. 13 (a) & (b) Source Voltage and Current after Converter ON and Source Voltage and Current-Transient

Fig. 14 Source Voltage and FFT

# **5. CONCLUSION**

BL-CSC Converter for BLDC Motor Drive is proposed in this paper. The proposed system is first designed in MATLAB simulation environment. The circuit modes of operation are elaborated and the simulation of the circuit is performed. The results are displayed and they show an improvement in power factor. The hardware prototype is implemented using FPGA board. The hardware results are also showing that the proposed system has successfully reduced the power factor problems. The system transients are also shown in the hardware results.

## REFERENCES

- Bist. V and Singh. B, (2014), 'An Adjustable Speed PFC Bridgeless Buck-Boost Converter Fed BLDC Motor Drive', IEEE Trans. Ind. Electron., Vol.61, No.6, pp.2665-2677.

- Bist. V and Singh. B, (2013), 'A Reduced Sensor PFC BL-Zeta Converter Based VSI Fed BLDC Motor Drive', Jr. Electric Power System Research, Vol.98, pp. 11–18.

- Bist. V and Singh. B, (2014), 'A PFC-Based BLDC Motor Drive Using a Canonical Switching Cell Converter,' IEEE Trans. Ind. Inform., Vol.10, No.2, pp.1207-1215.

- Chen. Y, Chiu. C, Jhang. Y, Tang. Z and Liang. R, (2013), 'A driver for the single-phase brushless DC fan motor with hybrid winding structure,' IEEE Trans.Ind. Electron, Vol. 60, No. 10, pp. 4369–4375.

- 5. Huang. X, Goodman. A, Gerada. C, Fang. Y and Lu. Q, (2012), 'A single sided matrix converter drive for a brushless DC motor in aerospace

*applications*,' IEEE Trans. Ind. Electron., vol. 59, no. 9, pp. 3542–3552.

- Kim. T.Y and Lyou. J, (2011), 'Commutation instant detector for the sensorless drive of BLDC motor,' IEEE Electronics Letters, Vol.47, No.23, pp.1269-1270.

- Lai. Y.S and Lin.Y.K, (2008), 'Novel Back-EMF Detection Technique of Brushless DC Motor Drives for Wide Range Control without Using Current and Position Sensors,' IEEE Trans. Power Electron., Vol.23, No.2, pp.934-940.

- Mohan. N, Undeland. T. M and Robbins W. P, (2000), *Power Electronics: Converters, Applications, and Design*. Hoboken, NJ, USA: Wiley, 2003. Limits for Harmonic Current Emissions (Equipment input current ≤16 A Per Phase), Int. Std. IEC 61000-3-2.

- Moreno. J, Ortuzar. M. E, and.Dixon. J. W, (2006), 'Energy-management system for a hybrid electric vehicle, using ultracapacitors and neural networks,' IEEE Trans. Ind. Electron., Vol. 53, No. 2, pp. 614–623.

- Ozturk. S. B, O. Yang. O and Toliyat. H. A, (2007), 'Power factor correction of direct torque controlled brushless DC motor drive,' in Conf. Rec. 42nd IEEE IAS Annu. Meeting, 23–27, pp. 297–304.

- Pillay. P and Krishnan. R, (1988), 'Modeling of permanent magnet motor drives,' IEEE Trans. Ind. Electron., Vol. 35, No. 4, pp. 537–541.

- Rahman. M. A and P. Zhou. (1996), 'Analysis of brushless permanent magnet synchronous motors,' IEEE Trans. Ind. Electron., vol. 43, no. 2, pp. 256– 267.

- Sago. O, Matsui. K, Mori. H, Yamamoto. I, Matsuo. M, Fujimatsu. I, Watanabe. Y and Ando. K, (2014), 'An optimum single phase PFC circuit using CSC converter,' Proc. of 30th IEEE-IECON, Vol.3, pp. 2684- 2689.

- Shao. J, Nolan. D, Teissier. M and Swanson. D, (2003), 'A novel microcontroller-based sensorless brushless DC (BLDC) motor drive for automotive fuel pumps,' IEEE Trans. Ind. Appl., Vol.39, No.6, pp.1734-1740.

- Singh. B and Singh. S, (2010), 'Single-phase power factor controller topologies for permanent magnet brushless DC motor drives,' IET Power Electron., Vol. 3, No. 2, pp. 147–175.

- Singh. B and Bist. V, (2013), "An Improved Power Quality Bridgeless Cuk Converter Fed BLDC Motor Drive for Air Conditioning System", IET Power Electron, Vol.6, No.5, pp. 902–913.

- Singh. B (2003) 'A review of single-phase improved power quality AC-DC converters,' IEEE Trans. Ind. Electron., Vol. 50, No. 5, pp. 962–981.

- Singh. B, Singh. S, Chandra. A and Al-Haddad. K, (2011), 'Comprehensive study of single-phase AC-

*DC* power factor corrected converters with highfrequency isolation,' IEEE Trans. Ind. Informat., Vol. 7, No. 4, pp. 540–556.

Su. G. J and McKeever. J.W, (2004), 'Low-cost sensorless control of brushless DC motors with improved speed range,' IEEE Trans. Power Electron., Vol.19, No.2, pp.296-302.