# CONTROL OF THREE PHASE FOUR WIRE ASYMMETRICAL FIFTEEN LEVEL INVERTER USING HYBRID BI-TRI DIMENSIONAL SPACE VECTOR PULSE WIDTH MODULATION

# K.ESWARAMOORTHY<sup>1\*</sup>, Dr. V.K. SHUNMUGHANAATHAN<sup>2</sup>

<sup>1\*</sup>Research Scholar, Anna University, Chennai, Tamilnadu, India. keswaramurthi@gmail.com

<sup>2</sup>Professor, Excel Engineering College, Namakkal, Tamilnadu, India. shunmughanaathan@gmail.com

Abstract: In general the tri-dimensional space vector pulse width modulation has been widely used for control of three phase four wire system converters. In this paper, the output voltage of inverter has been generated by the grouping of two different control schemes. One is for abc coordinate-based reference voltage generation for proposed inverter half-bridge circuit, and other is equivalent reference voltage of abc in  $\alpha 60$  coordinate for proposed inverter full bridge circuit. A simple bidimensional scheme calculated the generated gating signal of reference voltage vector location. The proposed scheme is verified by MATLAB/Simulink.

Keywords: Three Phase Four Wire System, abc,  $\alpha 60$ , Space Vector Pulse Width Modulation, Multilevel Inverter.

### I. INTRODUCTION

In three phase four wire system three-leg inverter configuration have been more popular in electrification building blocks for electrical drives, power compensators, conventional and renewable energies, Flexible AC Transmission Systems (FACTS), and office automation etc.. This is due to simple to control and achieve the magnitude of voltage and frequency by using pulse width modulation (PMW) techniques. The conventional multilevel inverter(MLI) topologies such as neutralpoint clamped, flying cascaded and Cascaded Hbridge are required more power semiconductor devices, voltage unbalancing problem, power devices and switching losses[1-2]. The fourth wire or the neutral wire current in this multilevel inverter topologies are generated due to unbalanced voltage and voltage stress across the inverter. The asymmetrical cascaded MLI topology is most popular to obtain the same output voltage level than the conventional MLI due to the lesser number of power semiconductor devices and other power components.

Numerous PWM techniques are used to control the MLI topologies. Space vector pulse width modulation (SVPWM) is widely implemented over the other techniques due to simple to achieve the desired output voltage, more switching voltage vectors, lower percentage of harmonics, switching losses, simple to implement experimentally and the higher percentage of dc source voltage utilization [3-4]. Commonly, the  $\alpha\beta$  or abc oriented SVPWM algorithms can be utilised to determine the reference voltage. The  $\alpha\beta$  coordinate is only appropriate for balanced or three wire applications, whereas abc coordinate was considered for four wire or unbalanced system [5-7].

The  $\alpha\beta$  coordinate SVPWM is the merits of simple to the determine calculation of reference voltage vector and location. This method is not suitable for control the voltage unbalanced load or source conditions [8]. The abc coordinate SVPWM useful to control the voltage or current when the unbalanced loads or sources. This scheme is simple to implement experimentally when the number output voltage level is higher than three [9]. Even though, the  $\alpha\beta0$  coordinate is superior performance when the output voltage level is lesser than three. The features of the  $\alpha\beta0$  and abc coordinate oriented SVPWM algorithms are combined to make the proposed SVPWM algorithm [10-12].

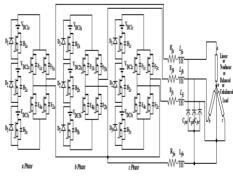

In this paper, three phase asymmetrical fifteen level inverter is proposed as shown in Fig.1.The half bridge circuit is controlled by abc coordinate or tri-dimensional SVPWM, whereas  $\alpha\beta0$  or tri-dimensional SVPWM control half-bridge circuit. The simple bi-dimensional SVPWM algorithm determines the reference voltage vector, and duty cycles are computed by using tri-dimensional SVPWM. The MATLAB/Simulink is carried to validate the proposed algorithm.

Fig. 1. Asymmetrical Fifteen level inverter

# II. Proposed Hybrid Bi-Tri Dimensional SVPWM

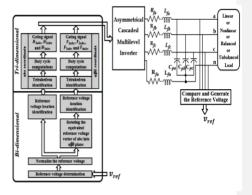

The Fig. 2 shows that the proposed block diagram of asymmetrical fifteen level inverter with the unbalanced nonlinear load. The reference voltage vector and duty cycle determination in abc coordinate of the half-bridge circuit are presented in this section. Also, the full bridge reference voltage vector and duty cycle determination in  $\alpha\beta0$  coordinate were presented in this section.

Fig. 2 Block diagram proposed HBTD-SVPWM

#### A. SVPWM in abc coordinate system:

In this section, the reference voltage vector was calculated by the bi-dimensional procedure in abc coordinate system. Tri-dimensional abc coordinate system computed the tetrahedron and duty cycle.

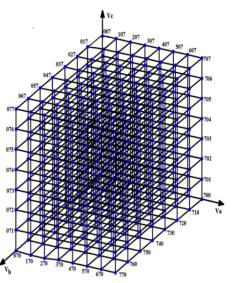

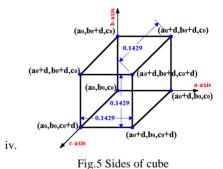

# i. Size of cubes determination

The voltage sources or output voltage levels in the multilevel inverter have defined the size of cubes in the abc coordinate. The sides of a cube are equal when the output voltage increment of the level is remaining unchanged. In this proposed asymmetrical multilevel inverter, the level of increment in the output voltage from one to other is same while the input sources are unequal as shown in Fig. 3.

The proposed inverter maximum voltage level

is

$$V_{DC1}+V_{DC2}+V_{DC3}=V_{DC}$$

. (1)

The output level switching in positive and negative direction is

(2)

$$V_0 = \frac{\pm m V_{DC}}{\pi}$$

#### Fig. 3 abc Coordinate Cubic SVPWM

From the cubic diagram Fig. 3 the number voltage vector points depend on the number of level of an inverter, i.e.,  $n^3$ , where n is indicated the number of inverter output level. Similarly, the number of subcubes is based on the number of levels, and it is calculated by  $(n-1)^3$ .

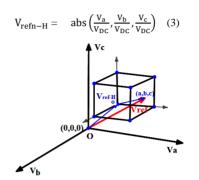

#### ii. Reference Voltage Vector Determination

The required output voltage vector is calculated from the actual voltage by comparing and adjusting with the output voltage of the inverter. The normalised reference voltage vector location is determined by an absolute value of phase reference voltage as shown in Fig. 4. The normalised reference voltage of H –bridge circuit is

Fig.4 Reference Voltage Vector Location.

### iii. Finding sub prism and Sides of Cube

Initially, the sub-prism was determined to find the sides of the cube. The  $V_{ref-H}O$  or new origin point is determined from the phase reference voltage absolute value. The point of reference voltage vector from the new origin location is calculated by

$$oa = V_{an} - abs (V_{ref-H}a)$$

$$ob = V_{bn} - abs (V_{ref-H}b)$$

$$oc = V_{cn} - abs (V_{ref-H}c)$$

(4)

The new origin is  $(a_0, b_0, c_0)$  and other sides of cubes are equalled in distance from the new origin location. In this proposed inverter, the sides of the cube are d=0.1429. The remaining sides are determined by as per the Fig. 5 of  $(a_0+d, b_0, c_0)$ ,  $(a_0, b_0, c_0+d)$ ,  $(a_0, b_0+d, c_0)$ ,  $(a_0+d, b_0+d, c_0)$ ,  $(a_0, b_0+d, c_0+d)$ .

Commented [G1]: Inserted: i

#### v. Finding the Tetrahedron from cube

The reference voltage vector area can be effortlessly calculated by min, median and max value estimation of reference voltage separate from the sub-3D square starting point. In this proposed method, the reference voltage vector laid simple two steps calculation determines tetrahedron. The calculating step procedure is same when the number of levels is changed. The following flowchart explains the determination reference voltage vector located tetrahedron.

Fig.6 Flowchart of abc coordinate SVPWM

#### vi. Duty cycle computation

The tetrahedron has four corner points, and duty cycles are computed from the points of abc phase voltage. The voltage vector of tetrahedron points are

From the voltage equation of tetrahedron, the duty cycles are computed to generate the

# pulses

$$d_1 + d_2 + d_3 + d_4 = 1 \tag{6}$$

The general equation is required to compute the voltage vector of any tetrahedron. To simply the above voltage vector equation the maximum, median and minimum value voltage vector is required in a tetrahedron,

$$K_{1} = max (a, b, c)$$

$$K_{2} = median (a, b, c)$$

$$K_{3} = min (a, b, c)$$

$$(7)$$

The duty cycle of any tetrahedron is

$$\begin{array}{c} d_{1} = 1 - K_{1} \\ d_{2} = K_{1} - K_{2} \\ d_{3} = K_{2} - K_{3} \\ d_{4} = K_{3} \end{array}$$

(8)

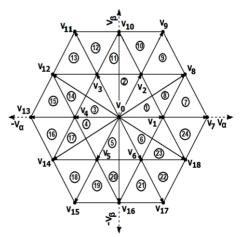

#### B. SVPWM in αβ0 coordinate system:

In this section, the reference voltage vector was calculated by the bi-dimensional procedure in abc coordinate system. Tri-dimensional  $\alpha\beta0$  coordinate system computed the tetrahedron and duty cycle.

#### i. Reference Voltage vector computation

The reference voltage vector calculation is same for abc and  $\alpha\beta\sigma$  coordinate.

$$V_{ref} = \sqrt{\frac{2}{3}(V_{Fa} + aV_{Fb} + a^2V_{Fc})} \quad (9)$$

where

$$a = e^{\frac{j2\pi}{3}}$$

and  $a^2 = e^{-j(\frac{2\pi}{3})}$

The reference voltage vector is abc coordinate system, and it is not suitable for the full bridge circuit. The full bridge circuit is generating the bidirectional or the positive and negative cycle output. The abc coordinate is not a reliable and wider control when the reference is positive and negative magnitudes. In this proposed scheme, the abc coordinate reference voltage is rotated to equivalently as a  $\alpha\beta\sigma$  coordinate. Hence, the reference voltage vector magnitude is same in both coordinate system, and it avoids the Clark's

transformation of the reference voltage.

$$V_{ref} = \left[ i \sqrt{\frac{2}{3}} \left( F_a - \frac{1}{2} F_b - \frac{1}{2} F_c \right) + j \frac{1}{\sqrt{2}} (F_b - F_c) + k \frac{1}{\sqrt{3}} (F_a + F_b + F_c) \right]$$

(10)

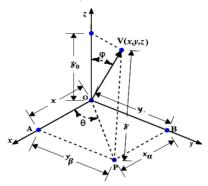

# ii. Rotating and identifying the reference voltage vector

Rotating the reference voltage vector from abc to  $\alpha\beta\sigma$  coordinate is

$$V_{\alpha\beta o}^{ref} = \begin{bmatrix} \frac{2}{3} & \frac{1}{3} & \frac{1}{3} \\ 0 & 1 & -1 \\ \frac{-\sqrt{2}}{3} & \frac{\sqrt{2}}{3} & \frac{\sqrt{2}}{3} \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(11)

The reference voltage vector may lay anyone of the triangle in  $\alpha\beta o$  coordinate as shown in Fig.7.

Fig. 7 Tri-dimensional SVPWM in αβ0 coordinates

To reduce the computational steps reference voltage vector location is determined by bidimensional coordinate. The reference voltage vector in  $\alpha\beta\sigma$  coordinate as shown in Fig. 8 and bidimensional value are

$$x_{\alpha} = int \left( V_{\alpha}^{ref} \right) \tag{12}$$

$$y_{\beta} = int \left( V_{\beta}^{ref} \right)$$

(13)

$$x_{\alpha} = r \cos \theta = V_{ref} \sin \varphi \cos \theta$$

(14)

$$y_{\beta} = r \sin \theta = V_{ref} \sin \varphi \sin \theta$$

(15)

$$z_{\alpha} = V_{ref} \sin \varphi$$

(16)

Where,

$$r = V_{ref} \sin \varphi$$

Fig. 8 Reference voltage vector calculation

# iii. Duty cycle Computation

The reference voltage vector location is identified from the eqn.The triangle is determined based the reference voltage vector location. The triangle edges are detected, and the duty cycle is computed as per the Fig. 9.

$$V_{ref} = t_1 V_1 - t_2 V_2 - t_3 V_3 \tag{17}$$

$$t_0 = 1 - t_x - t_y - t_z \tag{18}$$

Fig. 9 Duty cycle calculation

# III. SIMULATION RESULTS AND DISCUSSIONS

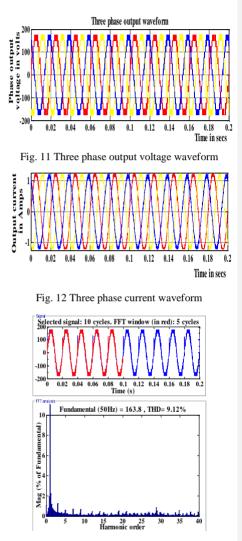

In this section, the proposed three phase four wire system for asymmetrical fifteen level inverter was simulated using MATLAB/Simulink as shown in Fig. 10. The nonlinear unbalanced load RL is connected across the output of inverter through the line. Fig. 11 and Fig. 12 are shows that the simulated three-phase output voltage and current waveform of an inverter. The voltage waveform is very smooth stepped output, and it has carried very minor distortion. The current waveform is nearly sinusoidal due to an inductive load connected and reduces the harmonics in the output waveform. Even though the phase output voltage of inverter has presented a smaller quantity of harmonics in the FFT spectrum. The fundamental output voltage is 163.8 and % THD is 9.12 as shown in Fig. 13. The utilisation of dc source and switching losses are not much efficient due to unsymmetrical switching sequences.

Fig. 10 Simulink model of HBTD-SVPWM

Fig. 13 Harmonic Spectrum of output voltage

# **IV. CONCLUSION**

The proposed hybrid bi-tri dimensional space vector pulse width modulation for asymmetrical fifteen level inverter with unbalanced nonlinear in three phase four wire system was simulated. The performance of inverter with mathematically developed algorithm was validated through the simulation. The reference voltage vector was computed in Bi-dimensional SVPWM. The tetrahedron and duty cycles are calculated by the simple procedure in Tri-dimensional SVPWM. The simulated results explained the lower percentage of THD and distortions. Even though, the THD values are higher than the standard value.

#### References

- J. Rodríguez, J. S. Lai, and F. Z. Peng, (Multilevel inverters: A survey of topologies, controls, and applications). IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, 2002.

- M. Ucar, E. Ozdemir, (Control of a 3-Phase 4-leg active power filter under non ideal mains voltage condition), Electric Power Systems Research, vol. 78, no. 1, pp: 58–73, 2008.

- Eswaramoorthy, K and Vijay, S.: (Analysis and Implementation of PV Cell-based thirteen level Multilevel Inverter with Carrier PWM Technique)., In: IJIRSET,vol.4,spl, issue, 13,pp.105-110,2015.

- Wei S and Wu B, (A general space vector PWM control algorithm for multilevel inverters). Eighteenth Annual. IEEE Appl. Power Electron. Conf. Expo. 2003. APEC '03., vol. 1, no. 1, pp. 562– 568, 2003.

- X. Yang, C. Wang, L. Shi, and Z. Xia, (Generalized space vector pulse width modulation technique for cascaded multilevel inverters). Int. J. Control Autom., vol. 7, no. 1, pp. 11–26, 2014.

- Xiaodong, Y., Chonglin, W., Liping, S. and Zhenglong, X., (Generalized space vector PWM method for cascaded multilevel inverters). Trans. of China Electrotechnical Society, vol. 29, no.6, pp.145-152,2014.

- Eswaramoorthy, K. and Shunmughanaathan, V.K.: (A Simple And Geometry Based Fast Space-Vector Pwm Technique For 15 Level Cascaded Multilevel Inverter With Reduction Of Switches). Asian Journal of Research in Social Sciences and Humanities, vol. 6, no.10, pp. 2305-2320, 2016.

- Gupta A. K and Khambadkone A. M, (A general space vector PWM algorithm for multilevel inverters, including operation in overmodulation range).IEEE Trans. Power Electron., vol. 22, no. 2, pp. 517–526, 2007.

- Eswaramoorthy K and Shunmughanaathan V K, (Digital Implementation of SVPWM in Over Modulation for Fifteen Levels MLI), Int. J. Printing,

Packaging & Allied Sciences., vol.4., no.5., pp. 3787-3799,2016.

- Chebabhi, A., Fellah, M.K. and Benkhoris, M.F., (Control of the Three Phase four-wire four-leg SAPF Using 3D-SVM Based on the Two Methods of Reference Signals Generating CV and SRF in the dq0-axes). Journal of Electrical Engineering, vol.1,no.1, pp.32-39,2015.

- Dai, N.Y., Lam, C.S., Wong, M.C. and Han, Y.D., (Application of 3D direct PWM in parallel power quality compensators in three-phase four-wire systems). In Power Electronics Specialists Conference, PESC 2008. IEEE, pp. 3220-3225, 2008.

- Chebabhi, A., Fellah, M.K., Benkhoris, M.F. and Kessal, A., (*Three Level Four Leg Shunt Active Power Filter Based a New Three Dimensional Space Vector Modulation strategy in the αβ0-axes*)., Journal of Electrical Engineering, vol.15, no.1, pp.39-45, 2015.