#### Buletinul Ştiinţific al Universităţii "Politehnica" din Timişoara

## Seria ELECTRONICĂ și TELECOMUNICAȚII TRANSACTIONS on ELECTRONICS and COMMUNICATIONS

Tom 53(67), Fascicola 1, 2008

# **About Modulation Strategies in Single-Phase Flying Capacitor Multilevel PWM Inverter**

Adrian Şchiop<sup>1</sup>, Viorel Popescu<sup>2</sup>

Abstract – In this paper the modulation strategies for single-phase multilevel PWM inverter with flying capacitors are analyzed. Some of the modulation strategies give self balancing voltage of flying capacitors, others do not.

The analyzed strategies are: phase disposition PWM method, phase-shifted PWM method, the saw-tooth rotation PWM method and the carrier redistribution PWM method. The results are obtained through simulation..

Keywords: flying capacitor, single-phase multilevel PWM inverter, modulation strategies

#### I. INTRODUCTION

Recently, multilevel inverters have received increased interest in the research and industrial community because of several advantages: reduced voltage stress on every switch because of using the series connection of power semiconductor devices, better power quality in comparison to two level PWM, smaller output filter.

Multilevel inverters are generally classified as diodeclamping inverters, flying capacitor inverters and cascade inverters [1]. The cascade inverter gives high flexibility in ex-tending the converter to more levels as well as minimizing its total harmonic distortion (THD), therefore requiring less output filtering. The cells of the cascade inverter can be realized by using single phase flying capacitors cell. By using cells with flying capacitors the number of levels at the output of cascade inverters will be greater than in the case when classical cell are used.

In the flying capacitor multilevel inverter, one of the most important issues is the balancing control of flying capacitor voltage. The voltage unbalancing of flying capacitor generates distortion of the output voltage and load current. Moreover, it causes breakdown of the switching device. Several modulation techniques for three phase flying capacitor are presented in the literature [1-8]. Some of these techniques obtain natural volt-age balancing for the flying capacitor like: phase-shifted PWM method, saw-tooth rotation PWM method and carrier

redistribution PWM method while for phase disposition PWM method the redundancy states are chosen for voltage balancing.

In this paper a comparison between the four methods is made for single phase flying capacitor regarding THD. The influence on the THD of the disposition of the carrier signals is also investigated.

### II. DESCRIPTION OF FLYING CAPACITOR MULTILEVEL INVERTER

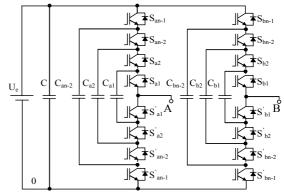

For the n level flying capacitor inverter the two switches  $S_{xi}$  and  $S_{xi}$  from Fig. 1 are driven complementary. An inverter leg may be represented as in Fig. 2.

Fig. 1. Scheme of the n level flying capacitor inverter.

Fig. 2. Modeling of inverter leg flying capacitor multilevel inverter.

We will say that two transistors  $S_{xk}$  and  $S_{xk}$  form a switching cell xk, with  $x \in \{a, b\}$ , k=1...n-1. For the *n* level flying capacitor inverter there will be *n*-1 switching cells. Let us define the connection functions

<sup>&</sup>lt;sup>1</sup> Universitatea din Oradea, Catedra de Electronică,

str. Universității, Nr.1, 410087, Oradea, Romania, e-mail aschiop@uoradea.ro

<sup>&</sup>lt;sup>2</sup> Universitatea Politehnica din Timișoara,

Facultatea de Electronică și Telecomunicații, Departamentul Electronică Aplicată, Bd. V. Pârvan Nr. 2, 300223 Timișoara, Romania, e-mail viorel.popescu@etc.upt.ro

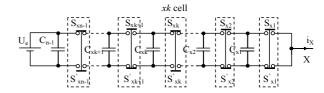

$y_{xk}$  for each switching cell. For example, for xk cell from Fig. 2,  $y_{xk}$ =1 when  $S_{xk}$  is in ON state and  $y_{xk}$ =0 when  $S_{xk}$  is in OFF state. Depending on adjacent switching states of the capacitor, the current through, for example  $C_{xk}$ , is ix when  $S_{xk+1}$  and  $S_{xk}$  are in ON state, -ix when  $S_{xk+1}$  and  $S_{xk}$  are in ON state, or zero when  $S_{xk}$  and  $S_{xk+1}$  are in ON state, or when  $S_{xk}$  and  $S_{xk+1}$  are in ON state. Consequently, adequate driving of the adjacent transistors can modulate the current through  $C_{xk}$ . In [9] it was shown that natural voltage balancing occurred when  $y_{xk}$  and  $y_{xk+1}$  have equal durations for each time period  $T_p$ .

Obtaining the equal durations of all connection functions of commutation cells for an inverter leg is possible by using n-1 carrier signals with a  $T_p/(n-1)$  phase shift between them, or by using carrier redistribution PWM method or the saw tooth rotation PWM method [1-4]. In [9] the expression of phase voltage for flying capacitor n level inverters depending on connection functions is derived:

$$u_{X0} = y_{xn-1}u_{Cxn-1} + \sum_{k=1}^{n-2} (y_{xk+1} + y_{xk})[(1 - y_{xk+1}) + (1 - y_{xk})](-1)^{(1 - y_{xk})}u_{Cxk}, (1)$$

$$X = \{A, B\}; x = \{a, b\}.$$

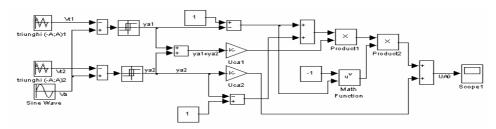

Fig. 3. Simulink model for one leg of the three level flying capacitor inverter.

The Simulink model for three level capacitor clamped inverter obtained by particularizing (1) for three level is presented in Fig. 3 [9]. All possible switching states for that inverter are shown in Table I.

TABLE I. ALL POSSIBLE SWITCHING STATES FOR SINGLE-PHASE THREE LEVEL FLYING CAPACITOR

|                    | Switching States |     |                 |                 |

|--------------------|------------------|-----|-----------------|-----------------|

| Output             | $S_{a2}$         | Sal | S <sub>b2</sub> | S <sub>b1</sub> |

| Ue                 | 1                | 1   | 0               | 0               |

|                    | 1                | 0   | 0               | 0               |

| $U_e/2$            | 1                | 1   | 0               | 1               |

| U <sub>e</sub> /2  | 0                | 1   | 0               | 0               |

|                    | 1                | 1   | 0               | 0               |

|                    | 0                | 0   | 0               | 0               |

|                    | 1                | 1   | 1               | 1               |

| 0                  | 1                | 0   | 1               | 0               |

| U                  | 0                | 1   | 0               | 1               |

|                    | 0                | 1   | 1               | 0               |

|                    | 1                | 0   | 0               | 1               |

|                    | 0                | 1   | 1               | 1               |

| -U <sub>e</sub> /2 | 0                | 0   | 1               | 0               |

| -002               | 1                | 0   | 1               | 1               |

|                    | 0                | 0   | 0               | 1               |

| -U <sub>e</sub>    | 0                | 0   | 1               | 1               |

When not using equal durations of all connection functions of commutation cells for an inverter leg, the switching states that will be used in capacitor voltage balancing in the leg a, for example, are shown in Table II [10].

TABLE II. SWITCHING STATES USED IN CAPACITOR VOLTAGE BALANCING IN LEG A

|                    |                          |                   | Switching states |     |                 |                 |

|--------------------|--------------------------|-------------------|------------------|-----|-----------------|-----------------|

| Output<br>voltage  | Capacitor voltage        | Output<br>current | S <sub>a2</sub>  | Sal | S <sub>b2</sub> | S <sub>b1</sub> |

| $U_{ca}>U_{e}/2$   |                          | I>0               | 0                | 1   | 0               | 0               |

|                    | $U_{ca}>U_e/2$           | I<0               | 1                | 0   | 0               | 0               |

| U <sub>e</sub> /2  | $U_e/2$ $U_{ca} < U_e/2$ | I>0               | 1                | 0   | 0               | 0               |

|                    |                          | I<0               | 0                | 1   | 0               | 0               |

| -U <sub>e</sub> /2 | I>0                      | 0                 | 1                | 1   | 1               |                 |

|                    | $U_{ca}>U_e/2$           | I<0               | 1                | 0   | 1               | 1               |

|                    |                          | I>0               | 1                | 0   | 1               | 1               |

|                    | $U_{ca} < U_e/2$         | I<0               | 0                | 1   | 1               | 1               |

#### III. MODULATION METHODS

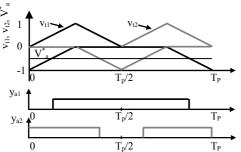

In the PWM method, the connection functions  $y_{xk}$  are obtained by comparison of the carrier signals with the modulating signals. The case when the carrier signals are overlapping and are covering a continuous range (mode A) and the case when the carrier signals are phase shifted between them (mode B) are analyzed. When the carrier signals are overlapped there are two opera-tion sub-modes: A1 when using 2(n-1)triangular carrier signals overlapping, (n-1) carrier signals for one leg and the other (n-1) for the other leg, and sub-mode A2 when using (n-1) carrier signals for both legs and two modulating signal phase shifted by T/2, where T is the period of output voltage. For mode B there are three sub-modes: B1 when carrier signals are triangular and phase shifted between them, B2 saw-tooth rotation PWM method that uses in fact saw-tooth carriers signal and B3 carrier redistribution PWM method that is using as carrier signals a sum of triangular and trapezoidal signals.

#### A. A1 Mode

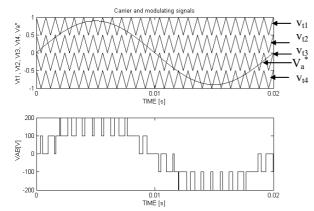

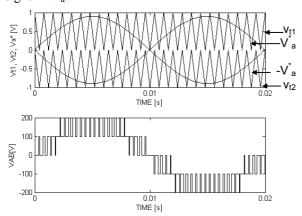

In A1 mode 2(n-1) in phase carrier signals and a modulating signal common for the two legs are used. The A1 mode is presented in Fig. 4 for the three level inverter.

The signal  $v_{t1}$  is used as carrier signal for the switching cell formed by  $S_{a2}$  and  $S_{a2}$ ,  $v_{t2}$  for  $S_{a1}$  and  $S_{a1}$  switching cell,  $v_{t3}$  for  $S_{b1}$  and  $S_{b1}$  switching cell and  $v_{t4}$  for  $S_{b2}$  and  $S_{b2}$  switching cell. In this case the natural voltage balancing is not realized because the time lengths resulted by comparison of  $v_{t1}$  with modulating signal  $V_a^*$  are not equals with those resulted by comparison of  $v_{t2}$  with the modulating signal  $V_a^*$ .

Fig. 4. A1 mode modulation in single phase three level inverter.

#### B. A2 Mode

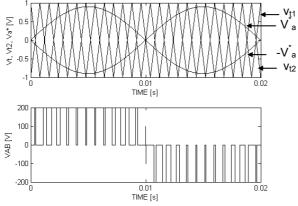

A2 mode for the three level inverter is presented in Fig. 5. The two carrier signals  $v_{t1}$  and  $v_{t2}$  are common for two legs. They can be in phase or phase opposition. Two modulating signals phase shifted by  $\pi$  are used. When the carrier signals are in phase opposition, Fig. 6, the natural voltage balancing occurs and the time length resulted by comparison of  $v_{t1}$  with modulating signal  $V_a^*$  is equal with that resulted by comparison of  $v_{t2}$  with the modulating signal  $-V_a^*$ .

Fig. 5. A2 mode modulation whit in phase carrier signals for single phase three level inverter.

Fig. 6. A2 mode modulation whit phase opposition carrier signals for single phase three level inverter.

Form Fig. 6 one can observe that when carrier signals are in phase opposition the number of line voltage levels decreases in comparison to the case when carrier signals are in phase.

#### C. B1 Mode

For B1 mode the way in which the phase shifted between carrier groups for the two legs influences the THD and the harmonic distribution will be studied.

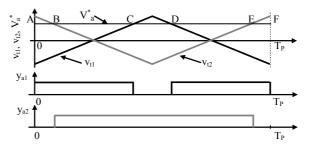

In the case of the three level flying capacitor the two carrier signals,  $v_{t1}$  and  $v_{t2}$ , are  $T_P/2$  phase shifted. Fig. 7 presents the carrier signals, modulator signal and connection functions for three level capacitor flying inverter for one leg. The connection functions are  $y_{a1}$  and  $y_{a2}$ ,  $V_a^*$  is the modulator signal and it is assumed constant for switching time  $T_p$ .

In Fig. 7 the sum of segments AB and EF is equal with CD. The lengths of these segments correspond to the time at which the connection functions yield the zero value. So, for this modulation type the time length of the connection functions are equal and voltage balancing for the flying capacitors is provided.

Fig. 7. B1 mode modulation for single phase three level inverter.

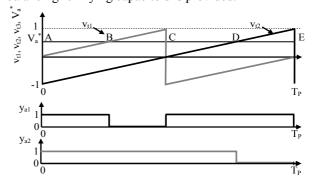

# D. B2 Mode Saw Tooth Rotation PWM Method Saw-tooth rotation PWM method presented in [2], [3] consists after all in using the (n-1) saw-tooth carrier signals phase shifted by $T_P/(n-1)$ . In this case, like in previous, the segments determined by cross point between carrier signals $v_{t1}$ , $v_{t2}$ and modulator signal $V_a^*$ , BC and DE from Fig. 8, are equal and voltage balancing for flying capacitors is provided.

Fig. 8. B2 mode modulation for single phase three level inverter.

#### E. B3 Mode Carrier Redistribution PWM Method

Carrier redistribution method is treated in [4], [5], [11-12]. Briefly, in this method for a switching cell, a sum of triangular and trapezoidal signals, are used as carrier signal. For n level flying capacitor one triangular signal and n-2 trapezoidal signals are used. The carrier signals are phase shifted by  $T_P/(n$ -1).

In Fig. 9 the case when modulating signal  $V_a^*$  cross the carrier signals in the [-1 0] range is presented. As one can see the time moments when connection functions  $y_{a1}$ =0 and  $y_{a2}$ =0 are equal and the natural voltage balancing occurs.

Fig. 9. Carrier signal for a switching cell when carrier redistribution PWM method are used for three level inverter.

#### III. SIMULATION RESULTS

The methods previously presented are analyzed by simulation in Simulink environment regarding the harmonic content and total harmonic distortion factor (THD). The analyses are performed for single phase three level and four level flying capacitor. In the next figures the line voltage and its harmonics is presented.

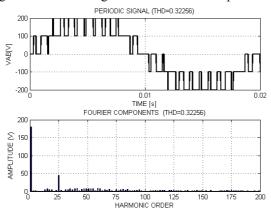

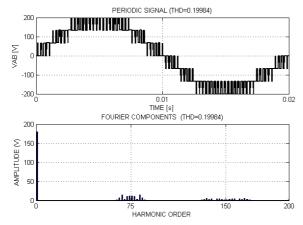

Fig. 10. A1 mode for single phase three level inverter.

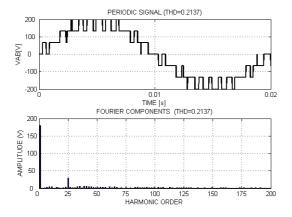

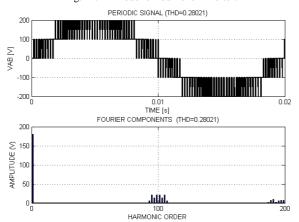

Fig. 11. A1 mode for four level inverter.

The Simulink model of the flying capacitor multilevel in-verter is realized using (1). The THD are calculated for the first 200 harmonics. The amplitude modulation

index is 0.9, the switching frequency is  $f_p$ =1250 Hz and DC link voltage  $U_e$ =200V. The frequency of the modulating signals is 50 Hz and the frequency modulation index is 25.

As one can see from Fig. 10 and Fig 11, for the A1 mode the harmonics are grouped around the frequencies multiple of the frequency modulation index.

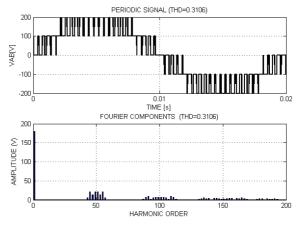

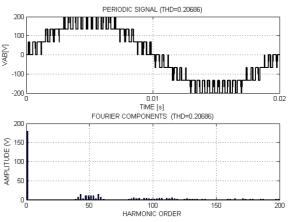

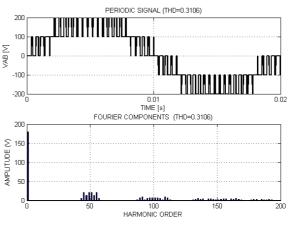

Fig. 12. A2 mode for three level inverter.

Fig. 13. A2 mode for four level inverter.

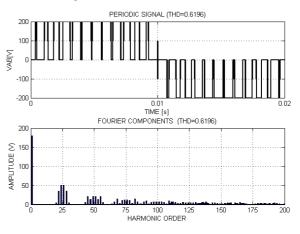

Fig. 14. A2 mode phase opposition for three level inverter.

For the A2 mode, when the carrier signals are in phase, the harmonics are grouped around twice of frequencies of mode A1. When the carrier signals are in phase opposition, Fig. 14, Fig. 15, the harmonics are grouped like in A1 mode. In this case the number

of line voltage levels decreases in comparison to the case when carrier signals are in phase.

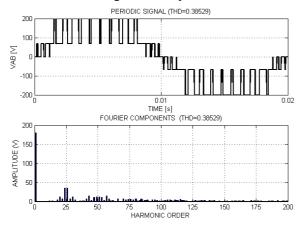

Fig. 15. A2 mode phase opposition for four level inverter.

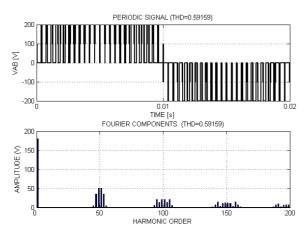

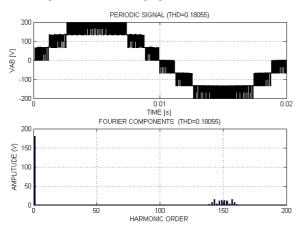

Fig. 16. B1 mode for single phase three level inverter.

Fig. 17. B1 mode for four level inverter.

For B1 mode, when the inverter has an odd number of levels, the number of levels of the output voltage decreases in comparison to the case when the group of carrier signals for inverter legs are  $90^{0}$  phase shifted. For B1 mode the harmonics of voltage line appear as side band of frequency  $f_{hB1}$ :

$$f_{hBI} = k(n-1)f_p; \ k \in N^*; \ for \ n \ odd,$$

$$f_{hBI} = 2k(n-1)f_p; \ k \in N^*; \ for \ n \ even.$$

(2)

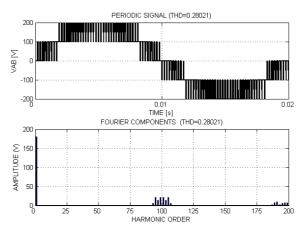

Fig. 18. B1 mode with 90° phase shifted between carrier groups for three level inverter.

Fig. 19. B1 mode with 90<sup>0</sup> phase shifted between carrier groups for four level inverter.

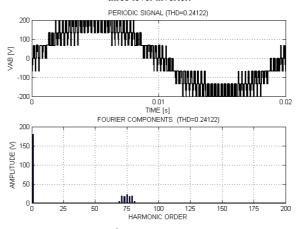

Fig. 20. B2 mode for three level inverter.

For B1 mode, when the carrier groups for the two legs are  $90^{0}$  phase shifted, the harmonics of voltage line appear as side bands of frequency  $f_{hB190PS}$ :

$$f_{hB190PS} = k(n-1)f_p; \ k \in N^*; \ for \ n \ even,$$

$$f_{hB90PSI} = 2k(n-1)f_p; \ k \in N^*; \ for \ n \ odd,$$

where  $n$  is the number of inverter levels. (3)

Fig. 21. B2 mode for four level inverter.

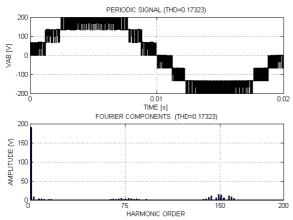

Fig. 22. B3 mode for three level inverter.

Fig. 23. B3 mode for four level inverter.

In B2 and B3 modes the harmonics appears as side bands of frequency  $f_{hB2}$  and  $f_{hB3}$

$$f_{hB2} = k(n-1)f_p, k \in N^*;$$

$$f_{hB3} = 2k(n-1)f_p, k \in N^*.$$

(4)

The THD for all analyzed cases are presented in Table III.

TABLE III THE THD VALUES OF LINE VOLTAGE

| mode         | 3 level | 4 level |

|--------------|---------|---------|

| A1           | 0.3225  | 0.2137  |

| A2           | 0.3106  | 0.2068  |

| A2 phase op. | 0.6196  | 0.3852  |

| B1           | 0.5915  | 0.1805  |

| B1 90° PS    | 0.2802  | 0.2412  |

| B2           | 0.3106  | 0.1998  |

| В3           | 0.2802  | 0.1732  |

From Table III we can observe that B3 mode leads to obtaining of lowest values of THD.

#### IV. CONCLUSIONS

In this paper the modulation strategies for singlephase cas-cade multilevel PWM inverter with flying capacitors are ana-lyzed. The characteristics of discussed PWM methods are as follows:

- A1 and A2 with phase opposition modes give the same harmonic distribution. The harmonics are grouped around the frequencies multiple of frequency modulation index.

- In A2 mode the harmonics are grouped around the twice frequencies multiple of frequency modulation index

- In B1, B2 and B3 modes the frequencies around which the side bands are grouped depend on the number of inverter levels.

- •B3 mode allows one to obtain the lowest values of THD

#### REFERENCES

[1] J. Rodriguez, J. S. Lai and F. Z. Peng "Multilevel Inverters: A Survey of Topologies, Controls and Applications," IEEE Trans. on Ind. Electron., vol. 49, no. 4,pp. 724–738, August 2002.

[2] B. S. Jin, W. K. Lee, T. J. Kim, D. W. Kang and D. S. Hyun, "A Study on the Multi-Carrier PWM Methods for Voltage Balancing of Flying Capacitor in the Flying Capacitor Multi-Level Inverter," Industrial Electronics Society, IECON 2005. 31st Annual Conference of IEEE pp. 721–726, 6-10 Nov. 2005.

[3] D.W. Kang, W.K. Lee and D.S. Hyun "Carrier-rotation strategy for volt-age balancing in flying capacitor multilevel inverter," IEE Proceedings of Electric Power Applications, -vol. 151, Issue 2, pp. 239–248. March 2004.

[4] D. W. Kang, B. K. Lee, J. H. Jeon, T. J. Kim, and D. S. Hyun "A Sym-metric Carrier Technique of CRPWM for Voltage Balance Method of Flying-Capacitor Multilevel Inverter," IEEE Trans. on Ind. Electron., vol. 52, no. 4, pp. 879–888, June 2005 .

[5] B. McGrath, T. Meynard, and G. Holmes, "Optimal modulation of flying capacitor and stacked multicell converters using a state machine de-coder," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 508–516, Mar. 2007.

[6] H. Wang, Y. Deng and X. He, "Novel Carried Based PWM Methor with Voltage Balance for Flying Capacitor Multilevel Inverters," 35th Annual IEEE Power Electronics Specialists Conference, Aachen, Germany 2004, pp. 4423–4427.

[7] X. Yuan, H. Stemmler and I Barbi, "Investigation on the Clamping Volt-age Self-Balancing on the Three Level Capacitor Clamping Inverter," Power Electronics Specialists Conference, 1999. PESC 99. 30th Annual IEEE vol 2, 1999, pp. 1059–1064.

[8] A. Schiop, "Simulink Model of Flying Capacitor Multilevel Inverter" OPTIM 2008.

[9] A. Şchiop, D. Trip "Simulink Models of Single Phase Multilevel Invert-ers" Conference Proceedings of National Symposium of Theoretical Electrical Engineering SNET'07, Bucuresti, 2007, pp. 254–260.

[10] M. Malinowski, S. Stynski, "Simulation of Single-Phase Cascade Multi-level PWM Converters," Proceedings of The International Conference on "Computer as a Tool" Eurocon 2007, Warsaw, September, 2007, pp. 1524–1529.

[11] J. Rodríguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro "Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives," IEEE Tran. on Ind. Electro., vol. 54, no. 6, pp. 2930–2945, De-cember 2007.

[12] D. W. Kang, Y. H. Lee, B. S. Suh, C. H. Choi, and D. S. Hyun, "An Improved Carrier-Based SVPWM Method Using Leg Voltage Redundancies in Generalized Cascaded Multilevel Inverter Topology," IEEE Tran. on Power Electron., vol. 18, no. 1, pp. 180–187, January 2003.